Tích hợp không đồng nhất, cơ hội cho phát triển lĩnh vực vi mạch bán dẫn tại Việt Nam

Make in Viet Nam - Ngày đăng : 08:49, 22/11/2021

Amkor là hãng đóng gói chip bán dẫn vi mạch hàng đầu thế giới và dự án đầu tư xây dựng nhà máy sản xuất đóng gói chip vi mạch bán dẫn thực sự là một tin rất vui cho ngành vi mạch bán dẫn của Việt Nam.

Từ nay tới năm 2035, Công ty Amkor Technology, Inc sẽ đầu tư vào tỉnh Bắc Ninh 1,6 tỷ USD để xây nhà máy sản xuất, lắp ráp và thử nghiệm vật liệu bán dẫn tại Khu công nghiệp Yên Phong II-C. (Ảnh: Công ty Amkor Technology, Inc có trụ sở chính tại Hoa Kỳ. (Nguồn: Amkor)

Cuộc khủng hoảng thiếu hụt chip vi mạch bán dẫn thời gian qua đã cho thấy tầm quan trọng của nhà máy sản xuất trong chuỗi giá trị và cung ứng, nhất là khi các công nghệ hiện đại tối tân nhất lại đang được đặt tại những nhà máy này. Vậy công nghệ đóng gói mức hệ thống SiP (System in Package) mà Amkor hứa hẹn mang tới Việt nam có điểm gi đặc biệt?

Kể từ khi Gordon Moore đưa ra phát biểu "số lượng transitor trên mỗi đơn vị diện tích vuông sẽ tăng lên gấp đôi sau mỗi hai năm" vào năm 1965, ngành công nghệ điện tử đã có những bước tiến dài trong việc tăng tỷ lệ tích hợp trên phiến bán dẫn. Đến gần đây khi kích thước transistor tiến tới kích thước nguyên tử thì người ta bắt đầu đặt dấu hỏi về tương lai của định luật Moore. Và SiP, công nghệ đóng gói chip thế hệ mới là một trong những câu trả lời.

Công nghệ tích hợp không đồng nhất là gì?

SiP đang hứa hẹn là một động cơ chính tiếp tục đẩy định luật Moore tiến về phía trước mở ra một kỷ nguyên phát triển mới của lĩnh vực vi mạch tích hợp. Để trả lời câu hỏi về SiP ở trên chúng ta hãy cùng tìm hiểu khái niệm tích hợp không đồng nhất (Heterogeneous Integration).

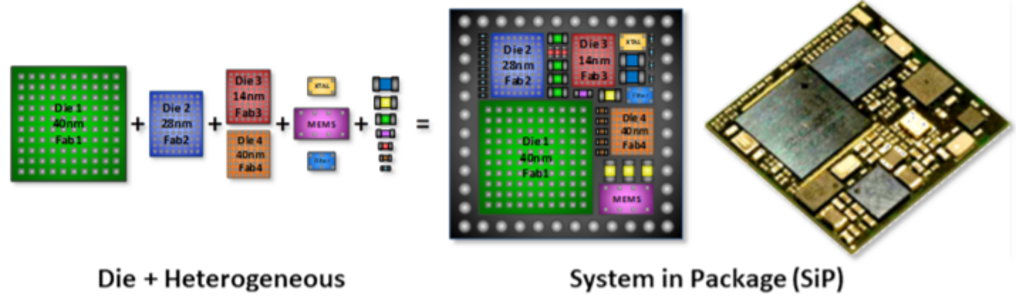

Tích hợp không đồng nhất nói tới kỹ thuật đóng gói những thành phần được sản xuất riêng biệt thành một thành phần mới duy nhất nhằm cải thiện tính năng, nâng cao hiệu quả hoạt động so với từng thành phần riêng lẻ.

Khái niệm này thật ra không mới, từ những năm 1970, khái niệm chip chứa nhiều module (multi chip module) đã khá phổ biến nhưng công nghệ đóng gói tiên tiến hiện nay đã cho phép đóng gói các mạch tích hợp được sản xuất ở các quy trình công nghệ khác nhau thành một chip riêng lẻ, trong đó có thể kể đến hai kỹ thuật điển hình là: Ball Grid Arrays (BGAs) và Through Silicon Vias (TSVs).

Nguồn: ASE

Ngày 14/7/1969, khi bước bước chân đầu tiên trên mặt trăng, Neil Armstrong đã nói "đây là một bước tiến nhỏ đối với con người nhưng là một bước nhảy vọt khổng lồ đối với nhân loại". Sự kiện này cũng bắt đầu thời kỳ phát triển rực rỡ của lĩnh vực mạch tích hợp.

Năm 2019 là năm đánh dấu kỷ niệm 50 năm ngày nhân loại đặt chân lên mặt trăng, cũng là năm mà báo cáo chuyên biệt về lộ trình kỹ thuật tích hợp không đồng nhất được tổ chức IEEE đưa ra. Điều đó nói lên rằng cộng đồng các chuyên gia trong ngành công nghiệp cũng như trong các viện, trường nghiên cứu xác định tích hợp không đồng nhất là kỹ thuật cần được ưu tiên cùng nhau hợp tác hơn là cạnh tranh để đẩy nhanh tốc độ phát triển của nó.

Bản báo cáo cung cấp cái nhìn toàn diện về bối cảnh và dự báo các yêu cầu công nghệ đối với sự phát triển của ngành công nghiệp điện tử trong 15 năm tới và nó cũng cung cấp tầm nhìn 25 năm về xu thế của kỹ thuật tích hợp không đồng nhất. (https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html)

Trước đây, các nhà máy sản xuất chip cơ bản có hai nhiệm vụ chế tạo chính, bao gồm: giai đoạn chế tạo lớp nền hình thành nên các linh kiện trên cùng một phiến bán dẫn (FEOL) và giai đoạn hình thành các lớp chứa các đường kết nối kim loại để kết nối các linh kiện thành mạch điện và chip hoàn chính (BEOL). Sau đó wafer được đưa tới nhà máy đóng gói chip, khi đó từng chip sẽ được cắt ra thành từng miếng, được đặt lên đế lớp vỏ của chip và nối dây từ bề mặt chip (miếng bán dẫn) ra chân của chip.

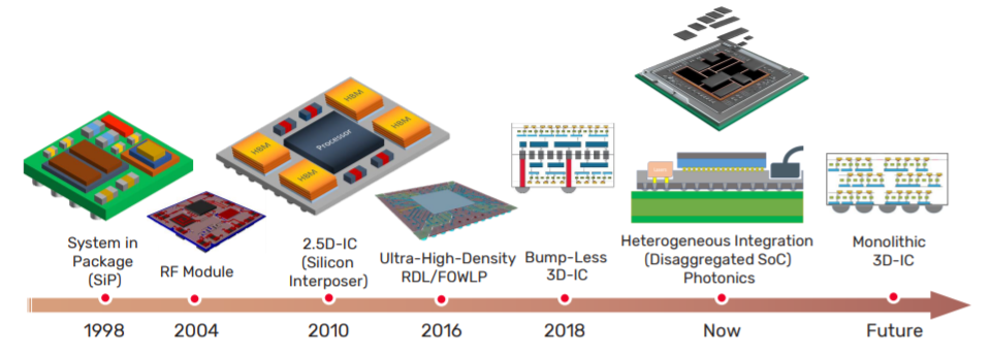

Ở mức chế tạo chip, tích hợp không đồng nhất gắn liền với khái niệm chiplet và Cadence đã khái quát hóa lịch sử và dự báo tương lai của công nghệ chipset như sơ đồ dưới đây:

Nguồn: Cadence

Theo đó, những kỹ thuật đóng gói tiên tiến hiện nay đã xóa nhòa ranh giới của nhà máy sản xuất chip (wafer fab) và cơ sở đóng gói chip (assembly.) Ở đó kỹ thuật kết nối các đường dẫn kim loại truyền thống trong các nhà máy sản xuất chip đã mở rộng tới việc kết nối ra chân của chip, cụ thể như các kỹ thuật wafer bumping, chế tạo via xuyên qua chiều dày wafer (TSV) chế tạo các lớp kết nối chuyên biệt (Inteposer), flip-chip... Việc này cũng đồng nghĩa kỹ thuật quang khắc không chỉ còn giới hạn được sử dụng trong các nhà máy sản xuất chip mà đã bắt đầu dịch chuyển sang lĩnh vực đóng gói chip.

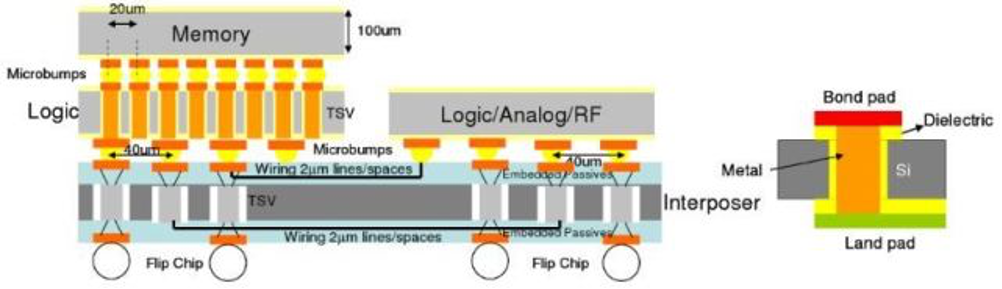

Hình ảnh dưới đây minh họa mức độ tích hợp mà kỹ thuật chế tạo via xuyên qua chiều dày wafer (TSV) có thể đem lại, ở đó bộ nhớ có thể đặt chồng lên các mạch logic tạo ra chip xử lý có diện tích nhỏ hơn; có thể tích hợp chip xử lý tín hiệu số và mạch tương tự và anten trên cùng một phiến bán dẫn được kết nối qua lớp interposer và sau đó các miro-bump có kích thước nhỏ theo tiêu chuẩn kỹ thuật của các tiến trình công nghệ tiên tiến trên tấm wafer gốc được trải rộng ra trên bề mặt đế của vỏ chip tới kích thước đủ lớn để các máy hàn mạch điện tử hiện đại có thể xử lý khi gắn chip lên các bảng mạch in.

Nguồn: Veeco Instruments

Công nghệ hứa hẹn mở ra một kỷ nguyên mới của định luật Moore

Vậy điều gì đã khiến cho kỹ thuật tích hợp không đồng nhất trở thành một xu hướng công nghệ cốt lõi hứa hẹn mở ra một kỷ nguyên mới của định luật Moore.

Đầu tiên, chúng ta hãy đề cập lại một chút về thuật ngữ yield. Tất cả chúng ta điều biết trong quá trình chế tạo trên cả tấm wafer, luôn luôn tồn tại một lượng sai hỏng nhất định, khi các tiến trình công nghệ cho phép mật độ tích hợp cực cao, diện tích chip trở nên lớn hơn đồng nghĩa tỷ lệ sai hỏng trên tấm wafer sẽ trở lên cao hơn trong khi giá thành sản xuất chip ở các tiến trình công nghệ tiên tiến không hề rẻ, dẫn tới sự không tối ưu về giá thành, điều này đặc biệt đúng khi chúng ta cố gắng tích hợp mọi thứ trên cùng một tiến trình công nghệ.

Thứ hai, không phải mọi chức năng đều đạt hiệu quả tốt nhất khi sử dụng tiến trình công nghệ tiên tiến nhất, bộ nhớ sẽ đạt hiệu quả cao khi sử dụng tiến trình công nghệ tiên tiến nhất nhưng các mạch xử lý tín hiệu tương tự thì lại không thực sự hiệu quả khi sử dụng tiến trình công nghệ đó vì quá trình chuyển đổi một mạch xử lý tín hiệu tương tự sang tiến trình công nghệ tiên tiến là rất mất thời gian.

Thứ ba, kỹ thuật tích hợp không đồng nhất cho phép các kiến trúc sư sự linh hoạt cao trong việc xây dựng thử nghiệm các kiến trúc chip mới đáp ứng nhu cầu chuyên biệt hóa chức năng của các công nghệ mới hiện nay như trí tuệ nhân tạo (AI), thế hệ thông tin mới 5G, 6G, xe tự hành (autonomous vehicles), trung tâm dữ liệu lớn (data center), IoT,... Các kỹ sư không phải chờ đợi thiết kế lại mọi thứ, thay vào đó họ đã có trong tay tất cả mọi thành phần và họ có thể bắt đầu xếp lego. Sau đó quyết định thiết kế mới có khi chỉ là một miếng lego nào đó mà thôi.

SiP (đóng gói mức hệ thống) đã hiện thực hóa những ưu điểm của kỹ thuật tích hợp không đồng nhất các vi mạch tích hợp và điều tiếp theo là gì? là sự tích hợp không đồng nhất giữa vi mạch phần cứng và phần mềm? tại sao không? Khi điều đó được hiện thực hóa, các bạn hãy thử tưởng tượng SiP sẽ có thể làm được những gì?

Cuối cùng, SiP không hề phủ nhận sự phát triển của các tiến trình công nghệ tiên tiến mà SiP và sự phát triển của các tiến trình công nghệ tiên tiến đang là hai động cơ chính đẩy định luật Moore tiếp tục tiến về phía trước, ít nhất là trong một thập kỷ tới đây.

Cơ hội cho Việt Nam

Việc Amkor, công ty hàng đầu thế giới về lĩnh vực đóng gói và kiểm thử chip vi mạch bán dẫn quyết định đầu tư xây dựng nhà máy tại Việt Nam là minh chứng rõ ràng cho việc Việt Nam đang ngày càng tham gia sâu rộng hơn vào sân chơi vi mạch toàn cầu.

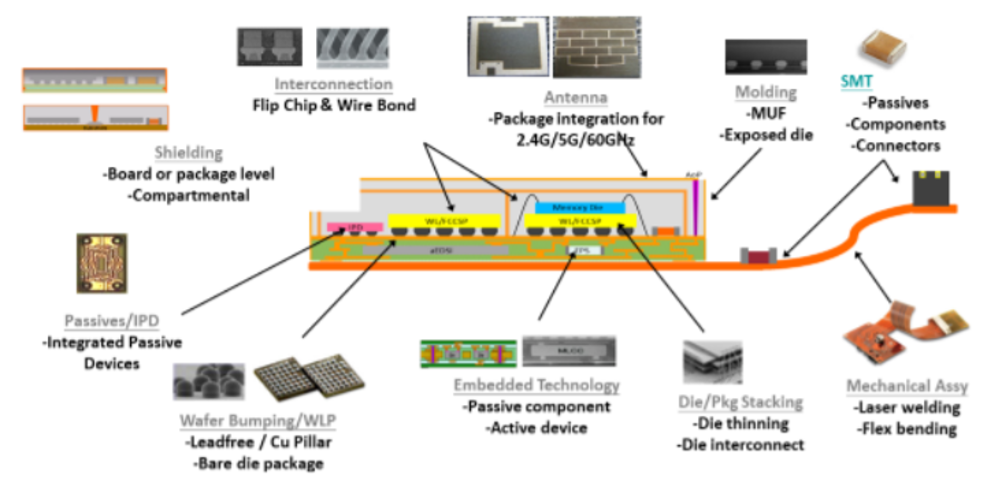

Tuy nhiên, điều này cũng đặt áp lực không nhỏ cho Việt Nam trong việc hoạch định chiến lược phát triển lĩnh vực công nghệ cao của quốc gia. Việt Nam có lợi thế nguồn nhân lực trẻ, dồi dào nhưng sân chơi vi mạch bán dẫn vẫn đang đứng trước thách thức thiếu hụt nguồn nhân lực có trình độ kỹ thuật cao. Thêm nữa, hệ sinh thái tích hợp không đồng nhất yêu cầu các nền tảng kỹ thuật khá đa dạng, lựa chọn nền tảng kỹ thuật đặc thù làm thế mạnh phát triển cho Việt Nam cũng sẽ đặt ra nhiều thách thức.

Các kỹ thuật trong hệ sinh thái tích hợp không đồng nhất. Nguồn: ASE

Chúng ta đang đứng trước rất nhiều cơ hội để phát triển lĩnh vực khoa học công nghệ cao, trong đó có lĩnh vực chip vi mạch. Tuy nhiên, để có thể tận dụng tối đa các cơ hội trong bối cảnh hội nhập quốc tế sâu rộng hiên nay, Việt Nam cần tích cực trong việc chủ động đón đầu xu thế và cần có quyết tâm chính trị lớn để có thể thống nhất và phát huy hiệu quả cao nhất từ sự hợp tác của tất cả các bộ, các tổ chức, và nguồn lực quốc gia.

Đặc biệt là vai trò của các trường đại học kỹ thuật đầu ngành của Việt Nam. Và làm sao để các bạn sinh viên có cơ hội tham gia các dự án gần với thực tế ngay khi còn học đại học ở Việt Nam vẫn còn là câu hỏi mở cần các nhà hoạch định chính sánh, nhà trường và doanh nghiệp cùng trao đổi và đưa ra các sáng kiến hành động ./.