Chiplets: Đổi mới ngành công nghiệp bán dẫn

Tạp chí online - Ngày đăng : 09:30, 09/07/2025

Chiplets: Đổi mới ngành công nghiệp bán dẫn

Ngành công nghiệp bán dẫn đang trải qua một cuộc cách mạng lớn nhờ vào sự phát triển của công nghệ chiplet. Được MIT Tech Review xếp hạng là một trong mười công nghệ đột phá của năm 2024, chiplet đã có bước tiến đáng kể trong thế giới bán dẫn.

Tóm tắt:

- Khái niệm chiplet: Chiplet là các mạch tích hợp mô-đun, chia nhỏ chức năng chip thành các thành phần chuyên biệt, kết nối trong một gói để tạo hệ thống linh hoạt.

- Khác biệt so với chip đơn khối: Không tích hợp tất cả chức năng vào một khuôn, chiplet tối ưu hóa từng thành phần riêng (CPU, GPU, bộ nhớ, I/O).

- Lợi ích chính: Cải thiện năng suất, giảm chi phí, tăng tính linh hoạt, cho phép tùy chỉnh và nâng cấp dễ dàng, phù hợp với các ứng dụng cụ thể.

- Công nghệ kết nối: Sử dụng UCIe và kỹ thuật đóng gói 2.5D/3D để đảm bảo băng thông cao, độ trễ thấp, hiệu quả năng lượng.

- Ứng dụng thực tiễn: Chiplet được áp dụng trong trung tâm dữ liệu, AI, HPC, IoT, viễn thông, ô tô, đáp ứng nhu cầu thiết bị mạnh mẽ, tiết kiệm năng lượng.

- Thách thức kỹ thuật: Tích hợp chiplet từ nhiều nguồn đòi hỏi tiêu chuẩn hóa giao thức, công cụ thiết kế, và giải quyết độ trễ, tiêu thụ điện năng.

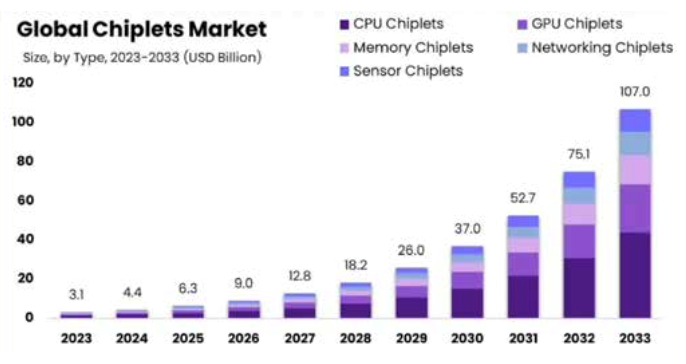

- Thị trường phát triển: Dự kiến tăng từ 3,1 tỷ USD (2023) lên 107 tỷ USD (2033) với tốc độ tăng trưởng 42,5% mỗi năm.

- Tiêu chuẩn hóa: UCIe và các tiêu chuẩn như IEEE 1838, P3405 đang phát triển, nhưng thị trường chiplet mở chưa hoàn thiện, cần vài năm nữa.

- Bảo mật chiplet: Tích hợp nhiều chiplet làm tăng nguy cơ tấn công phần cứng, đòi hỏi bảo mật mạnh hơn và truy xuất nguồn gốc.

- Vai trò của Việt Nam: Việt Nam có cơ hội mở rộng từ lắp ráp, kiểm thử sang thiết kế và đóng gói chiplet, nhờ đầu tư công nghệ và nhân lực.

- Hợp tác quốc tế: Cần chuyển giao công nghệ, hợp tác với các nước như Hàn Quốc, Đài Loan để nâng cao năng lực trong ngành bán dẫn.

- Thách thức của Việt Nam: Đối mặt với chi phí đầu tư cao, thiếu nhân lực chuyên sâu, và cạnh tranh từ các quốc gia có nền bán dẫn mạnh.

“Ý tưởng đằng sau chiplet là chia nhỏ và chinh phục”, Vidya Neerkundar, Giám đốc sản phẩm cho luồng DFT (Thiết kế để Thử nghiệm), giải pháp thử nghiệm silicon Tessent tại Siemens EDA cho biết. Thay vì sản xuất một con chip duy nhất với tất cả các tính năng tích hợp, chiplet cho phép các nhà thiết kế chia nhỏ các chức năng thành các thành phần rời rạc, mỗi thành phần đảm nhận một nhiệm vụ cụ thể: trong thiết kế chiplet, mỗi thành phần được tối ưu hóa cho một chức năng riêng biệt như xử lý, bộ nhớ hoặc đồ họa, và sau đó được tích hợp lại để tạo thành một hệ thống hoàn chỉnh.

Chiplet là gì?

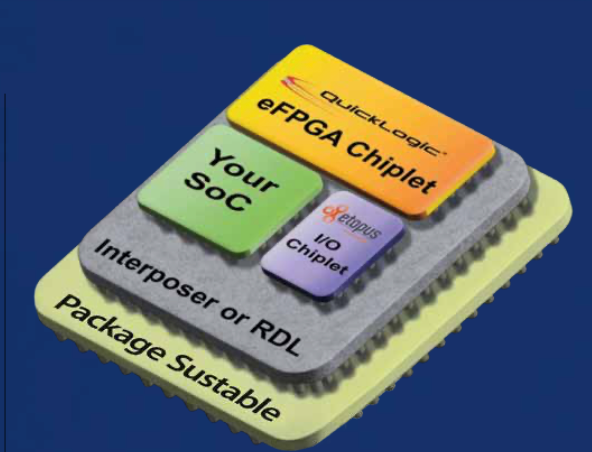

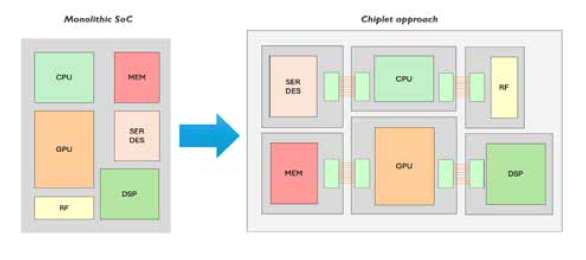

Chiplet là các mạch tích hợp mô-đun nhỏ có thể kết hợp để tạo ra hệ thống trên chip (SoC) hoặc thiết kế nhiều khuôn (die) phức tạp hơn. Không giống như các chip đơn khối truyền thống, tích hợp tất cả các chức năng vào một khuôn silicon duy nhất, chiplet chia nhỏ các chức năng này thành các đế chuyên dụng nhỏ hơn. Các chiplet này sau đó được kết nối với nhau trong một gói duy nhất, cho phép linh hoạt, hiệu quả và khả năng mở rộng cao hơn trong thiết kế chip.

Khái niệm chiplet đại diện cho sự thay đổi đáng kể trong ngành công nghiệp bán dẫn, giải quyết một số thách thức liên quan đến thiết kế chip đơn khối, chẳng hạn như hạn chế về năng suất, chi phí và hiệu suất. Bằng cách sử dụng chiplet, các nhà thiết kế có thể tối ưu hóa các thành phần riêng lẻ một cách độc lập, kết hợp và kết hợp các công nghệ khác nhau và đạt được mức hiệu suất cao hơn mà không cần phải thiết kế lại hoàn toàn.

Thiết kế dựa trên Chiplet

Chiplet cung cấp một hệ thống mô-đun kết hợp các chip riêng biệt từ nhiều nhà cung cấp và nút công nghệ khác nhau thay vì thiết kế tất cả các chức năng thành một hệ thống duy nhất trên chip.

Thiết kế dựa trên chiplet là câu trả lời khi chúng ta tiếp cận giới hạn vật lý của công nghệ dựa trên silicon truyền thống - Định luật Moore, đã thúc đẩy ngành công nghiệp bán dẫn trong những thập kỷ qua. Để đảm bảo tăng gấp đôi linh kiện trên mạch tích hợp hai năm một lần, các nhà sản xuất chip đã khám phá ra những cách để làm cho bóng bán dẫn nhỏ hơn và tích hợp nhiều hơn vào chip, tạo ra các thiết kế hệ thống trên chip (SoC) đơn khối có kích thước lớn.

Điện thoại di động là minh chứng cho sự thành công của thiết kế đơn khối, kết hợp các hàm toán học, màn hình, truyền thông không dây, âm thanh, v.v., tất cả thành một chip 100mm duy nhất. Tuy nhiên, việc mở rộng quy mô hơn nữa trở nên cực kỳ tốn kém để có được lợi thế hiệu suất tối thiểu. Do đó, ý tưởng là chia SoC lớn, phức tạp thành các chiplet nhỏ hơn và liên kết chúng lại với nhau để xây dựng một hệ thống cho các ứng dụng cụ thể. Phương pháp tiếp cận giống như Lego mang lại cho các nhà sản xuất sự linh hoạt để tạo ra một hệ thống tiết kiệm chi phí với chi phí đầu vào thấp hơn cho các thiết kế chip mới và hiệu quả và hiệu suất được tăng lên.

Chiplet hoạt động bằng cách tận dụng các công nghệ đóng gói tiêu chuẩn và tiên tiến cùng các kết nối tốc độ cao để tích hợp nhiều khuôn không đồng nhất hoặc đồng nhất vào một gói duy nhất. Chiplet được thiết kế như các khối xây dựng mô-đun, mỗi khối thực hiện một chức năng cụ thể. Ví dụ:

Chiplet CPU: Xử lý các tác vụ xử lý mục đích chung.

Chiplets GPU: Quản lý đồ họa và các tác vụ tính toán song song.

Chiplet bộ nhớ: Cung cấp khả năng truy cập bộ nhớ tốc độ cao.

Chiplet I/O: Quản lý các hoạt động nhập/xuất.

Một cách để chiplet đạt được sự tối ưu hóa là điều chỉnh công nghệ một cách chiến lược. Ví dụ, chiplet IO và bus sử dụng các nút kế thừa đáng tin cậy, trong khi chiplet tính toán sử dụng công nghệ tiên tiến để đạt hiệu suất cao nhất. Chiplet bộ nhớ áp dụng các công nghệ bộ nhớ mới, đảm bảo khả năng thích ứng với các nhu cầu bán dẫn đa dạng.

Chìa khóa cho một thiết kế chiplet thành công nằm ở công nghệ kết nối. Việc các chiplet có thành công trong việc theo kịp Định luật Moore hay không phần lớn phụ thuộc vào mức độ gần nhau của các chiplet trong một gói để đảm bảo kết nối điện nhanh, băng thông cao giữa chúng giống như các chức năng trong SoC đơn khối.

Các kết nối tốc độ cao, chẳng hạn như UCIe (Universal Chiplet Interconnect Express), cho phép giao tiếp hiệu quả giữa các chiplet. Các kết nối này đảm bảo băng thông cao, độ trễ thấp và hiệu quả năng lượng, giúp phương pháp chiplet khả thi cho các ứng dụng hiệu suất cao. Các kỹ thuật đóng gói tiên tiến, chẳng hạn như tích hợp 2.5D và 3D, được sử dụng để lắp ráp các chiplet trong một gói duy nhất. Các kỹ thuật này cho phép khoảng cách gần hơn giữa các chiplet, giảm khoảng cách mà tín hiệu cần truyền đi và cải thiện hiệu suất tổng thể.

Ngoài đóng gói tiên tiến, các kỹ thuật đóng gói tiêu chuẩn cũng được sử dụng trong các thiết kế nhiều khuôn. Đóng gói tiêu chuẩn liên quan đến các phương pháp lắp ráp và gồm các thành phần bán dẫn thông thường, có thể đặc biệt hữu ích cho một số loại ứng dụng nhất định. Ví dụ về đóng gói tiêu chuẩn bao gồm liên kết dây, flip- chip và khung dẫn. Đóng gói tiêu chuẩn cung cấp giải pháp đáng tin cậy và tiết kiệm chi phí để tích hợp chiplet, đặc biệt là trong các ứng dụng mà các kỹ thuật đóng gói tiên tiến có thể không cần thiết.

Một trong những lợi thế quan trọng nhất của công nghệ chiplet là khả năng tích hợp các thành phần không đồng nhất. Các nhà thiết kế có thể kết hợp các chiplet được chế tạo bằng các công nghệ quy trình khác nhau, chẳng hạn như kết hợp một chiplet logic hiệu suất cao với một chiplet bộ nhớ mật độ cao, để giúp tiết kiệm chi phí và tăng hiệu quả sản xuất.

Thiết kế và kiểm chứng các hệ thống dựa trên chiplet đòi hỏi các công cụ và phương pháp chuyên biệt. Các công cụ thiết kế phải hỗ trợ bản chất mô-đun của chiplet, cho phép tích hợp và tối ưu hóa dễ dàng từng thành phần. Các công cụ kiểm chứng rất quan trọng để đảm bảo rằng tất cả các chiplet hoạt động liền mạch với nhau, đáp ứng các tiêu chuẩn về hiệu suất và độ tin cậy cần thiết.

Chiplet so với Chip nguyên khối

Chiplet cung cấp một số lợi thế. Một lợi ích chính là cải thiện năng suất sản xuất. Các khuôn nhỏ hơn ít bị lỗi hơn, giúp giảm chi phí và tăng hiệu quả sản xuất. Chiplet cũng cho phép thiết kế linh hoạt hơn và khả năng mở rộng, cho phép các nhà sản xuất kết hợp các loại chiplet khác nhau (ví dụ: CPU, GPU, bộ nhớ) để tạo ra các giải pháp tùy chỉnh phù hợp với các yêu cầu cụ thể về hiệu suất và công suất. Sự tích hợp không đồng nhất này có thể dẫn đến các hệ thống mạnh mẽ và hiệu quả hơn.

Ngoài ra, các thiết kế dựa trên chiplet đẩy nhanh quá trình phát triển vì các chiplet lỗi thời có thể dễ dàng và thường xuyên được cập nhật.

Cuối cùng, các chiplet thường có tỷ lệ năng suất cao vì chúng thường nhỏ hơn với thiết kế đơn giản hơn, bắt đầu với các khuôn tốt sau khi đã thử nghiệm trước khi liên kết và chúng có thể dựa vào các chiến lược sửa chữa cho các kết nối bị lỗi.

Tuy nhiên, chiplet cũng có một số thách thức so với chip đơn khối. Sự phức tạp của việc kết nối nhiều chiplet có thể gây ra độ trễ và chi phí tiêu thụ điện năng, có khả năng ảnh hưởng đến hiệu suất. Cần có các công nghệ đóng gói và kết nối tiên tiến để giảm thiểu những vấn đề này, có thể làm tăng độ phức tạp trong thiết kế và sản xuất

Ngoài ra, để đạt được khả năng giao tiếp liền mạch giữa các chiplet đòi hỏi các tiêu chuẩn và giao thức mạnh mẽ, chẳng hạn như UCIe. Bất chấp những thách thức này, lợi ích của việc cải thiện năng suất, tính linh hoạt và khả năng mở rộng thường khiến chiplet trở thành lựa chọn hấp dẫn cho các thiết kế bán dẫn hiện đại.

Với những lợi ích vượt trội, chiplet đang trở thành một xu hướng quan trọng trong ngành công nghiệp bán dẫn và được nhiều công ty công nghệ hàng đầu như AMD, Intel, NVIDIA, TSMC và Apple áp dụng mạnh mẽ. Các trung tâm dữ liệu, điện toán hiệu suất cao (HPC) và trí tuệ nhân tạo (AI) là những lĩnh vực chính áp dụng chiplet.

Thị trường điện tử tiêu dùng, viễn thông và ô tô cũng đang ngày càng tận dụng chiplet để đáp ứng nhu cầu về các thiết bị mạnh mẽ và hiệu quả hơn. Sự phát triển của các thiết bị Internet vạn vật (IoT) đã thúc đẩy nhu cầu về chiplet trong các thiết bị điện tử tiêu dùng. Các thiết bị IoT yêu cầu các thành phần có thể xử lý và truyền dữ liệu với khối lượng lớn trong khi tiêu thụ ít điện năng hơn. Chiplet, hiệu quả hơn so với chip đơn khối truyền thống, rất phù hợp để đáp ứng các yêu cầu này.

Tương lai của chiplet: Viễn cảnh & Thách thức

Theo báo cáo mới nhất từ Markets.us, thị trường chiplet toàn cầu dự kiến sẽ tăng trưởng với tốc độ hàng năm trên 42%. Nghiên cứu đã xác định được 3,1 tỷ đô la doanh thu trong thị trường chiplet vào năm 2023, nhưng tất cả đều nằm trong các công ty riêng lẻ, 2/3 đến từ việc ra mắt bộ xử lý của Intel, AMD và Nvidia và phần còn lại đến từ các thiết bị mạng của Marvell và FPGA cao cấp của AMD/Xilinx. Thị trường chiplet dự kiến sẽ tăng trưởng lên 107,0 tỷ đô la vào năm 2033, tốc độ tăng trưởng kép CAGR là 42,5%, với 4,4 tỷ đô la được dự đoán cho năm 2024.

Chiplet cho phép các nhà thiết kế sản phẩm kết hợp và ghép các thành phần khác nhau, cho phép tùy chỉnh IC phù hợp với các ứng dụng cụ thể và sử dụng các công nghệ quy trình khác nhau.

Đây là nơi mà TSMC có ảnh hưởng lớn, họ đang tìm cách chuẩn hóa quy trình phát triển và kết hợp chiplet trên một chất nền. Các thiết bị không đồng nhất với chiplet từ các nhà cung cấp khác nhau hiện đang nổi lên để thúc đẩy tăng trưởng hơn nữa và có các dự án quan trọng của châu Âu để đảm bảo rằng công nghệ cho chiplet có sẵn trong khu vực trong một chuỗi cung ứng mở.

Thị trường cũng chứng kiến sự xuất hiện của các công ty chuyên về thiết kế, sản xuất và lắp ráp chiplet. Những công ty này cung cấp một loạt các kết nối, thiết bị và dịch vụ dựa trên chiplet, góp phần vào sự tăng trưởng của thị trường.

Ngoài ra, các công nghệ đóng gói tiên tiến và các giải pháp kết nối đã phát triển để cho phép tích hợp chiplet hiệu quả, tạo điều kiện cho giao tiếp băng thông cao và độ trễ thấp giữa các chiplet.

Chiplet cung cấp một bước nhảy vọt lớn về chức năng và năng suất bán dẫn, giống như IP mềm đã làm cách đây 40 năm, nhưng cần phải có nhiều thứ kết hợp lại với nhau trước khi điều đó trở thành hiện thực - Cần có một hệ sinh thái, mà hiện tại vẫn còn rất sơ khai. Nhiều công ty đã đạt đến giới hạn lưới (diện tích tối đa của một con chip có thể được in trong một lần sử dụng mặt nạ ảnh) và buộc phải chuyển sang các giải pháp đa đế, nhưng điều đó không tạo ra thị trường chiplet cắm và chạy (plug-and-play).

Một sự hiểu biết đầy đủ về hệ sinh thái này vẫn đang được phát triển. “Chúng tôi biết cách tạo ra các chiplet chuẩn”, Mark Kuemerle, Phó chủ tịch công nghệ và Giám đốc công nghệ của các giải pháp tùy chỉnh tại Marvell cho biết. “Nó được gọi là HBM (bộ nhớ băng thông cao) và là chiplet duy nhất hiện nay. Nó được định nghĩa trong JEDEC (nhóm công nghiệp toàn cầu phát triển các tiêu chuẩn mở cho vi điện tử). Tiêu chuẩn nêu rằng, Đây là các chiều x, y. Đây là cách bạn kết nối chúng. Bất kỳ ai cũng có thể xây dựng một thứ có thể giao tiếp với nó”.

Để tạo ra một thị trường chiplet mở, các công ty cần phải có cùng mức độ chuẩn xác. Điều này có vẻ không phải là một khái niệm mới lạ nhưng nếu có thể làm được điều này, nó có thể giúp việc chia sẻ trở nên khả thi.

Có thể mất nhiều thời gian hơn mọi người hy vọng. Mayank Bhatnagar, Giám đốc tiếp thị sản phẩm của SSG tại Cadence cho biết: “Các tiêu chuẩn vẫn đang phát triển. Các tiêu chuẩn như UCIe đang được áp dụng rộng rãi trong ngành và tôi tin rằng nó sẽ cất cánh, nhưng chúng ta vẫn còn cách xa điều đó vài năm nữa. Tôi không mong đợi điều đó xảy ra trong ba đến năm năm tới. Có lẽ phải đến những năm 2030, chúng ta mới bắt đầu thấy sự sẵn có của các chiplet tiêu chuẩn trong ngành”.

Một thách thức đáng kể là sự phức tạp về mặt kỹ thuật liên quan đến việc tích hợp và đảm bảo khả năng tương tác giữa các chiplet. Vì các chiplet đến từ các nhà sản xuất khác nhau và có thể có thiết kế và thông số kỹ thuật khác nhau, nên việc tích hợp chúng vào một hệ thống gắn kết có thể là một thách thức. Đảm bảo khả năng tương thích và giao tiếp liền mạch giữa các chiplet đòi hỏi phải lập kế hoạch cẩn thận và phát triển các giao diện và giao thức chuẩn hóa.

Hiện tại, các công ty đều có tiêu chuẩn riêng. Marc Swinnen, Giám đốc tiếp thị sản phẩm tại Ansys cho biết: “Hiện tại, mọi thứ giống như miền Tây hoang dã vậy. Điều này thật tốt. Hãy để hàng ngàn bông hoa nở rộ. Nhưng tôi nên sử dụng công nghệ đóng gói nào? Có rất nhiều lựa chọn khác nhau. Mỗi OSAT (công ty cung cấp dịch vụ đóng gói và kiểm tra linh kiện bán dẫn thuê ngoài) đều có công nghệ riêng, rồi đến các biến thể của những công nghệ đó, và không phải tất cả đều sẽ thành công. Sẽ có một sự thay đổi trong thị trường tại một thời điểm nào đó.

Không ai muốn đặt cược vào con ngựa thua và bị mắc kẹt với một số công nghệ kỳ quặc mà không ai khác sử dụng. Cần phải có sự hợp nhất trong ngành”.

Mặc dù tiêu chuẩn có thể hữu ích, nhưng có một khối lượng tới hạn. Kuemerle của Marvell cho biết: “Đã có rất nhiều sự phấn khích khi Intel khởi động nhóm UCIe. Với giao diện die-to-die, mọi người đều nghĩ rằng các chiplet thực sự sẽ cất cánh. Nhưng nó thực sự không thay đổi bất cứ điều gì. Lý do là có rất nhiều thứ khác cần thiết. Có rất nhiều sự phức tạp phát sinh từ việc kết nối những thứ này lại với nhau, chẳng hạn như thử nghiệm. Bạn phải tìm ra cách để các chiplet này giao tiếp với nhau, để chúng ta có thể có được phạm vi thử nghiệm tốt trên tất cả chúng”.

Các tiêu chuẩn này đang được nghiên cứu.

Neerkundar của Siemens cho biết: “Quay trở lại những năm 90, đã có IEEE1149.1, nói về cách mỗi chip có thể được kết nối với bo mạch. Có một ngôn ngữ quét biên - BSDL. Bây giờ có IEEE 1838, mô tả cơ chế PTAP-/STAP. Điều này mô tả cách cơ chế đó có thể được sử dụng trong IC 3D, trong ngăn xếp. Bạn cũng có thể sử dụng cơ chế đó trong 2.5D. Các tiêu chuẩn khác đang được đưa ra. P3405, là một tiêu chuẩn IEEE, nói về thử nghiệm và sửa chữa kết nối. Ngoài ra còn có P1838A, nói về giao diện quét ranh giới theo thuật ngữ IC 3D”.

Tiêu chuẩn thường tránh một số vấn đề nhất định khi không rõ ngành công nghiệp cần đi theo hướng nào. Bhatnagar của Cadence cho biết: “Tiêu chuẩn tránh định nghĩa những thứ có thể rất đa dạng. Ví dụ, UCIe không đưa ra định nghĩa nào về cách triển khai kênh. Intel là thành viên sáng lập và có công nghệ EMIB, nhưng tiêu chuẩn này tránh yêu cầu sử dụng bất kỳ công nghệ cụ thể nào. Nó định nghĩa những thứ về kênh, chẳng hạn như hàm truyền điện áp (VTF) và thông số kỹ thuật nhiễu xuyên âm. Chúng tôi đã thấy các kênh rất khó hiểu được tạo ra để đáp ứng các yêu cầu, nhưng trông rất khác so với những gì tiêu chuẩn ban đầu nghĩ đến”.

“Thách thức là ngành công nghiệp muốn có một tiêu chuẩn,” Prautsch của Fraunhofer nói.

“Họ muốn tiêu chuẩn hóa nó càng nhiều càng tốt. Nhưng họ không muốn có chi phí chung”. Và cũng giống như đối với IP mềm, cần phải có một bộ sản phẩm đi kèm với một chiplet cho phép nó được tích hợp thành công. “Chúng ta cần những mô hình nào?” Pratyush Kamal, Giám đốc giải pháp kỹ thuật trung tâm tại Siemens, đặt câu hỏi.

“Có một khoảng cách lớn mà ngành công nghiệp đang cố gắng giải quyết. TSMC có ngôn ngữ Khối 3D của họ và họ đang cố gắng công khai ngôn ngữ này trong IEEE. Những nỗ lực tương tự đang được tiến hành trong OCP (Open Computer Project), nhưng ngay cả ở đó, họ vẫn chưa xác định đầy đủ mọi thứ cần thiết. Lấy ví dụ về IC 3D, trong đó bạn có mạch tín hiệu hỗn hợp trải dài trên hai khuôn. Khi bạn cung cấp chiplet này, với hình thức vật lý, bạn vẫn cần cung cấp danh sách mạng SPICE liên kết với ngăn xếp đầy đủ để mô phỏng đầy đủ. Hầu hết thời gian, khi bạn thực hiện tích hợp chiplet, bạn không nhất thiết phải xem xét toàn bộ chiplet.

Chúng tôi trừu tượng hóa mọi thứ. Chúng tôi chỉ quan tâm đến ranh giới giao diện, nhưng sẽ có phân tích đòi hỏi phải có cái nhìn toàn diện về chiplet được trình bày cho trình biên dịch, cho nhà thiết kế đóng gói”.

Để đạt được nền kinh tế chiplet thị trường mở, Chakraborty của Synopsys lưu ý: “Khi bạn có nhiều chiplet đến từ các nguồn khác nhau, bạn phải thực hiện phân tích ở cấp độ hệ thống. Điều đó có nghĩa là bạn cần các mô hình để phân tích liên quan đến các chiplet đó. Ví dụ, chúng có thể là các mô hình nhiệt của chip. Tương tự như vậy, bạn cần các mô hình tiêu thụ điện năng để phân tích IR và EMIR. Sau đó, bạn có danh mục rộng này về ứng suất và ứng suất nhiệt cơ học, cần phải được phân tích. Bạn không thể thực sự phân tích điều đó ở cấp độ khuôn.

Vậy làm thế nào để bạn thực hiện điều đó ở cấp độ hệ thống, một tiêu chuẩn, trong khi bạn đang trộn và kết hợp các khuôn và giải pháp từ các nhà cung cấp khác nhau? Bảo mật cũng quan trọng, đặc biệt là khi bạn đang tái sử dụng các chiplet và giải pháp từ các nhà cung cấp khác. Làm thế nào để bạn đảm bảo tính bảo mật và tính toàn vẹn cho các chip của mình? Tất cả những điều đó đều rất quan trọng và phải kết hợp với nhau theo một cách đáng tin cậy”.

Việc thương mại hóa chiplet sẽ làm tăng đáng kể khả năng tấn công vào phần cứng, đòi hỏi các biện pháp và quy trình bảo mật rộng hơn nhiều ở mọi cấp độ của chuỗi cung ứng, bao gồm khả năng truy xuất nguồn gốc từ thiết kế ban đầu đến cuối vòng đời. Nhiều tiến bộ đã đạt được trong những năm gần đây về các biện pháp bảo mật, bao gồm từ việc xác định lưu lượng dữ liệu bất thường bên trong chip đến các kỹ thuật che giấu phức tạp. Nhưng chiplet làm tăng số lượng các vectơ tấn công có thể xảy ra và càng có nhiều chiplet trong thiết kế thì việc bảo vệ thiết bị càng khó khăn vì có nhiều dữ liệu được xử lý, di chuyển và lưu trữ hơn và nhiều thành phần hơn tham gia vào việc thực hiện điều đó.

Lee Harrison, Giám đốc giải pháp IC ô tô Tessent tại Siemens EDA cho biết: “Ngay cả khi tất cả các chiplet trong một thiết bị đều có một thành phần bảo mật, chẳng hạn như gốc tin cậy (RoT), thì cũng không có gì đảm bảo rằng chúng sẽ dễ dàng giao tiếp với nhau. Và điều này có nguy cơ làm tổn hại đến tính bảo mật tổng thể ở cấp độ thiết bị”.

Chiplet có cùng vấn đề bảo mật như bất kỳ chip nào khác. “Có 20 vectơ tấn công khác nhau, từ việc đánh cắp cơ sở dữ liệu, hối lộ những người trong nhóm thiết kế hoặc nhóm xác minh phân tích IR và EMIR. Sau đó, bạn có danh mục để chèn mạch độc hại hoặc chia sẻ bí mật thiết kế, cho đến các khía cạnh con người và liệu chip có bất kỳ bí mật nào bảo vệ thông tin bí mật hay không”, theo Scott Best, Giám đốc cấp cao, sản phẩm bảo mật silicon tại Rambus. “Kẻ tấn công muốn đánh cắp những bí mật đó, hoặc đảo ngược kỹ thuật các mạch bảo vệ chúng hoặc thực hiện một số loại kênh phụ phân tích năng lượng để gây rò rỉ thông tin ra khỏi chip. Có rất nhiều cách mà chip và chiplet đều có thể bị tấn công”.

Đồng thời, vấn đề phát sinh khi có nhiều chiplet được đóng gói cùng nhau. Scott Best, lưu ý: “Hầu hết các con chip không có đóng gói riêng. Nhưng giờ đây, chúng giống như những con chip có bạn cùng phòng. Đây là một vấn đề đóng gói thú vị khi không chỉ đóng gói một con chip riêng lẻ - nó phải giao tiếp với tất cả các bạn cùng phòng của mình, và sau đó một hoặc một số bạn cùng phòng sẽ giao tiếp với thế giới thực thông qua I/O, và điều đó trở nên thú vị”.

Dần dần, mọi thứ sẽ đi vào nề nếp. “Bạn không thể nói rằng các công cụ cần phải phát triển, hay tiêu chuẩn cần phải phát triển. Bạn cần phải có cả hai cùng phát triển”, Neerkundar nói. “Bạn cần có các tiêu chuẩn và công cụ hỗ trợ tiêu chuẩn. Sau đó, ngành công nghiệp có thể xem xét cách bạn có thể thiết kế các chiplet và mua các chiplet và lắp ráp chúng độc lập với nhà cung cấp A, nhà cung cấp B và nhà cung cấp C, rồi sau đó tạo ra những chiplet độc đáo của riêng bạn. Chúng ta vẫn chưa đạt đến trình độ đó”.

Kết luận

Công nghệ chiplet đang nổi lên như một xu hướng trọng tâm trong ngành công nghiệp bán dẫn toàn cầu, và Việt Nam đang từng bước tiếp cận lĩnh vực này như một cơ hội chiến lược để nâng cao vị thế trong chuỗi giá trị công nghệ cao.

Hiện tại, Việt Nam chủ yếu tham gia vào các công đoạn lắp ráp, đóng gói và kiểm thử vi mạch. Tuy nhiên, sự phát triển của công nghệ chiplet - cho phép tích hợp nhiều chip nhỏ (chiplet) vào một hệ thống lớn thay vì thiết kế nguyên khối - mở ra cơ hội để Việt Nam mở rộng vai trò từ “hậu cần” sang tham gia sâu hơn vào khâu thiết kế và tích hợp hệ thống. Hướng phát triển cụ thể bao gồm đầu tư vào công nghệ đóng gói tiên tiến (như 2.5D và 3D), phát triển nguồn nhân lực chất lượng cao, tăng cường hợp tác quốc tế để tiếp nhận chuyển giao công nghệ, cũng như xây dựng chính sách ưu đãi mạnh mẽ từ chính phủ nhằm hỗ trợ doanh nghiệp trong nước.

Dù vậy, Việt Nam vẫn đối mặt với nhiều thách thức như chi phí đầu tư cao, thiếu hụt nhân lực chuyên sâu và sự cạnh tranh gay gắt từ các quốc gia có nền tảng bán dẫn mạnh như Hàn Quốc, Đài Loan hay Trung Quốc. Nếu có chiến lược phát triển bài bản và bền vững, Việt Nam hoàn toàn có khả năng tận dụng được xu thế chiplet để từng bước vươn lên trong ngành công nghiệp bán dẫn toàn cầu.

Với những bước tiến này, chiplet hứa hẹn sẽ trở thành tiêu chuẩn mới trong thiết kế vi mạch, mở ra cơ hội phát triển các hệ thống điện tử mạnh mẽ, linh hoạt và tiết kiệm chi phí hơn trong tương lai. Đây không chỉ là một sự thay đổi về mặt công nghệ, mà còn là một bước ngoặt quan trọng đối với ngành công nghiệp bán dẫn, định hình lại cách thức sản xuất và phát triển vi mạch trong nhiều năm tới.

Tài liệu tham khảo:

1. https://ictc.edu.vn/chiplets-doi-moi-nganh-cong-nghiep-

ban-dan/

2. https://semiengineering.com/development-flows-for-

chiplets/

3. https://www.synopsys.com/glossary/what-are-chiplets.html

4. https://www.imec-int.com/en/articles/chiplets-piecing-

together-next-generation-chips-part-i

5. https://www.eenewseurope.com/en/boom-predicted-for-

chiplet-market/#:~:text=The%20global%20chiplet%20

market%20is,this%20was%20withing%20single%20

companies

(Bài đăng ấn phẩm in Tạp chí TT&TT số 5 tháng 5/2025)