Hệ thống trên chip (SoC - System on Chip) ra đời được xem như một giải pháp khắc phục nhược điểm của SoB, tất cả các thành phần được thiết kế trên một chip duy nhất. SoC tích hợp cao mang lại các lợi ích như chi phí thấp, kích thước vật lý nhỏ, trọng lượng nhẹ và tiêu thụ điện năng thấp, tạo điều kiện thuận lợi cho việc hiện thực hóa các thiết bị di động nhỏ gọn. Tuy nhiên, vấn đề chính của SoC là tích hợp anten trên chip – OCA (On-Chip Antenna) khi mà kích thước của nó tỷ lệ với bước sóng. Hệ thống 5G sử dụng bước sóng mmWave dẫn tới kích thước anten nhỏ gọn là điều kiện thuận lợi để sử dụng OCA. Mặc dù vậy, thiết kế OCA vẫn đối mặt với một số thách thức sẽ được phân tích chi tiết trong bài báo này.

Ảnh minh hoạ

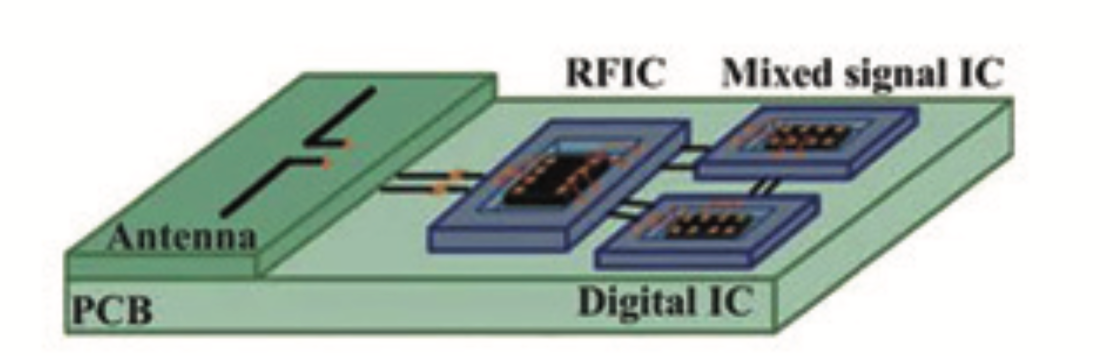

Hện nay, phương pháp phổ biến nhất để xây dựng một hệ thống vô tuyến là thông qua việc ghép nối các thành phần rời rạc như mạch tích hợp kỹ thuật số (IC), IC trộn tín hiệu (Mixed signal IC), IC tần số

vô tuyến (RFIC) và các thành phần thụ động trên bảng mạch in PCB (Printed Circuit Board) (Hình 1). Phương pháp này được gọi là hệ thống trên bo mạch SoB (System on Board)[1]: các IC riêng biệt được gắn trên PCB, mỗi IC yêu cầu đóng gói cồng kềnh và đắt tiền để bảo vệ vật lý; các kết nối đầu vào - đầu ra từ bộ chip đến bo mạch hệ thống sử dụng các tấm liên kết (bond pads) trên chip và dây liên kết (bond wires) làm hạn chế hiệu suất và độ tin cậy của chip. Dẫn tới hệ thống tổng thể theo phương pháp này có kích thước lớn và chi phí thực hiện cao. Ngoài ra, vì nhiều loại IC khác nhau được sử dụng cho một hệ thống, nên các quy trình thiết kế và chế tạo khác nhau, điều này gây ra các vấn đề về tính tương thích và độ tin cậy. Ngoài IC, anten được thiết kế trên một PCB riêng biệt, phải được tích hợp với các IC và các thành phần rời khác. Trong một số trường hợp, anten có thể nằm trên cùng một PCB với các vi mạch. Anten này được kết nối với RFIC thông qua các dây liên kết và tấm liên kết, điều này tạo ra thêm suy hao chèn RF và truyền dẫn kém tin cậy hơn. Để giải quyết các vấn đề trên, giải pháp tốt nhất là kết hợp tất cả các thành phần rời rạc trên một chip duy nhất, hay được gọi là hệ thống trên chip - SoC[2].

Trong vài thập kỷ qua, các bóng bán dẫn oxit kim loại bổ sung (CMOS) được thu nhỏ đáng kể, đã thúc đẩy sự phát triển của vi mạch lên mức tích hợp cao hơn, giúp tích hợp hệ thống hoàn chỉnh trên một chip duy nhất. SoC tích hợp cao mang lại lợi ích như chi phí thấp, kích thước vật lý nhỏ, trọng lượng nhẹ và tiêu thụ điện năng thấp, tạo điều kiện thuận lợi cho việc hiện thực hóa các thiết bị di động nhỏ gọn, chẳng hạn như cảm biến IoT (Internet of Things) và hệ thống radar nhỏ gọn. Do sự phát triển nhanh chóng của vi mạch, mô-đun kỹ thuật số, mô-đun tương tự và đầu cuối RF có thể được tích hợp trên một chip duy nhất. Tuy nhiên, một số vấn đề vẫn tồn tại trong việc kết hợp tất cả các mô-đun khác nhau trong một chip. Mỗi mô-đun mạch yêu cầu quy trình chuyên biệt riêng của nó. Nếu tất cả các mô-đun mạch được tích hợp trong một chip, quá trình này có thể không phù hợp để tất cả chúng hoạt động tốt nhất, và thách thức lớn nhất với một SoC vô tuyến thực sự là việc tích hợp một anten nên chip. Kích thước chip điển hình từ vài mm2 đến khoảng 100 mm2. Tuy nhiên, kích thước anten tỷ lệ thuận với bước sóng, khá lớn ở tần số thấp.

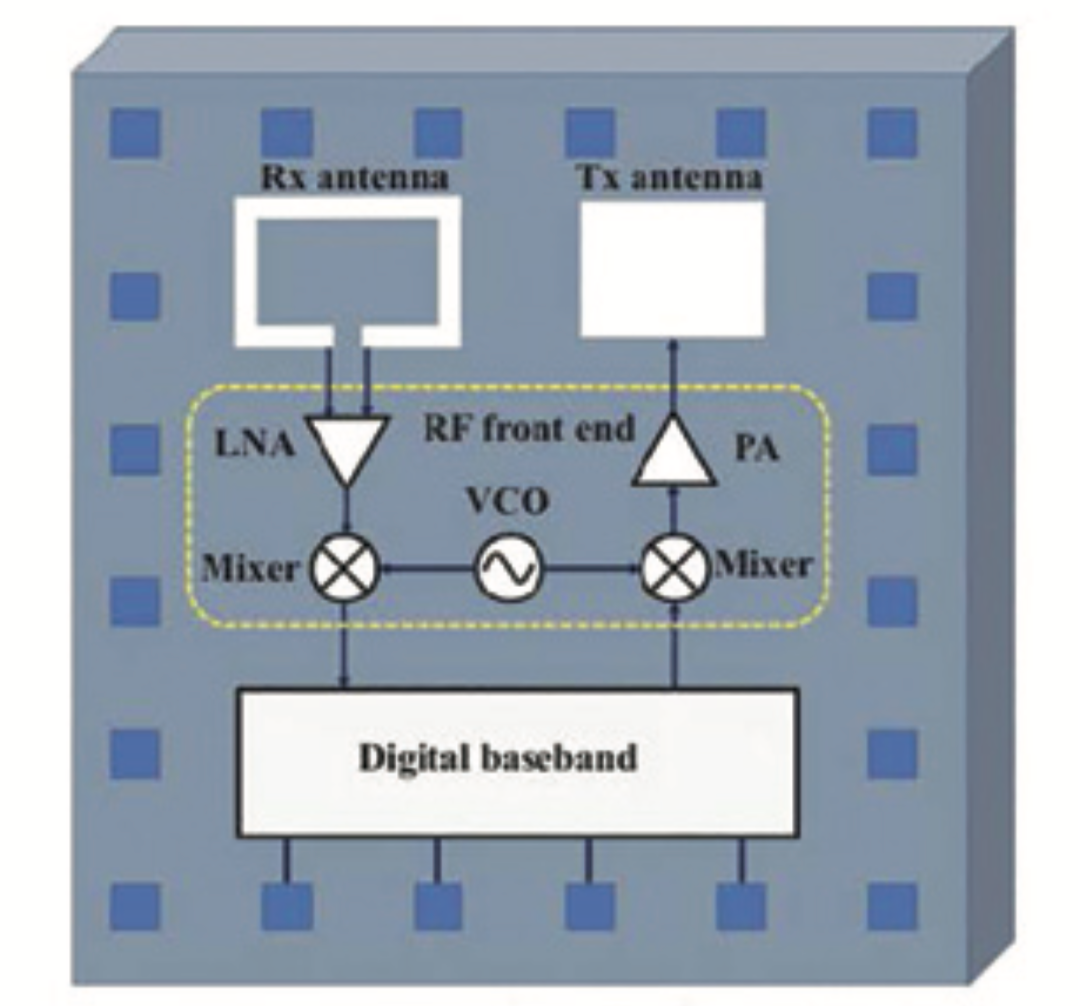

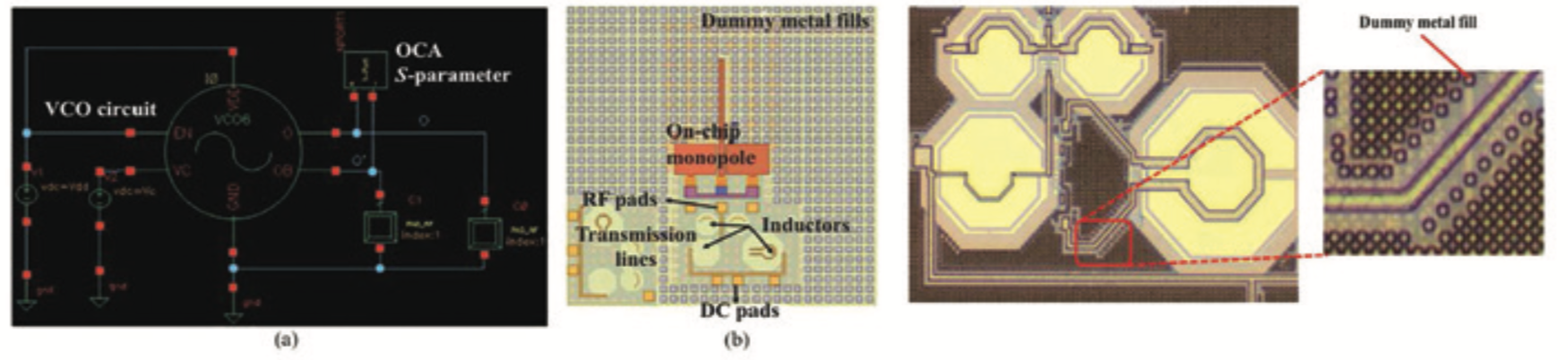

Do đó, kích thước anten điển hình lớn hơn nhiều so với kích thước của không gian chip có sẵn cho các ứng dụng tần số thấp. Ví dụ, chiều dài anten WiFi thông thường là khoảng 60mm, vì vậy nó không thể được thực hiện một cách hiệu quả trên chip. Hơn nữa, sau khi tích hợp tất cả các mô-đun mạch, không gian hạn chế để thực hiện OCA. Trong hai thập kỷ qua, do nhu cầu cao về băng thông và tính nhỏ gọn của hệ thống, những nỗ lực to lớn đã được thực hiện trong việc phát triển các ứng dụng sóng milimet (mm-wave) và sub-terahertz. Việc sử dụng các dải tần sóng mm và sub-terahertz đã làm giảm đáng kể kích thước anten (do bước sóng ngắn hơn), mang lại khả năng triển khai OCA. Hình 2 minh họa khái niệm tích hợp OCA với IC. Vì OCA có thể được cấp nguồn bởi mạch thông qua một đường truyền trên chip, ảnh hưởng của các dây liên kết và tấm liên kết có thể được loại bỏ. Hơn nữa, việc tích hợp OCA và các mạch trong cùng một chip loại bỏ hạn chế của việc phối hợp trở kháng 50 Ω. Thay vào đó, các phương pháp phối hợp trở kháng linh hoạt hơn có thể được áp dụng, cung cấp cho các nhà thiết kế vi mạch và anten tự do thiết kế hơn. Tuy nhiên, rất khó để thiết kế một OCA với hiệu suất cao trên chip. Nhiều thách thức liên quan đến OCA vẫn cần được giải quyết.

Hình 1. Hệ thống PCB tích hợp với RFIC, IC trộn tín hiệu, IC kỹ thuật số và anten PCB riêng biệt

Hình 2. Khái niệm về hệ thống tích hợp trên chip - SoC

Thách thức trong thiết kế OCA

OCA là một giải pháp tuyệt vời cho các ứng dụng yêu cầu mức độ tích hợp cao hơn và chi phí thấp hơn. Việc hiện thực hóa OCA trong các quy trình CMOS thương mại là khả thi. Tuy nhiên, vẫn còn nhiều thách thức liên quan đến OCA. Trong phần này, các thách thức của OCA được nghiên cứu từ các khía cạnh thiết kế, bố cục và đo đạc.

1. Ngăn xếp CMOS không tương thích

Silicon dạng khối là chất nền được sử dụng phổ biến nhất trong các quy trình CMOS tiêu chuẩn. Nó có điện trở suất thấp và rất thích hợp cho các mạch. Sự phong phú của nó đảm bảo chi phí thấp hơn cho các quy trình CMOS. Tuy nhiên, các đặc tính vật liệu của silicon và sự xếp chồng của CMOS không phù hợp để thực hiện hiệu quả các OCA.

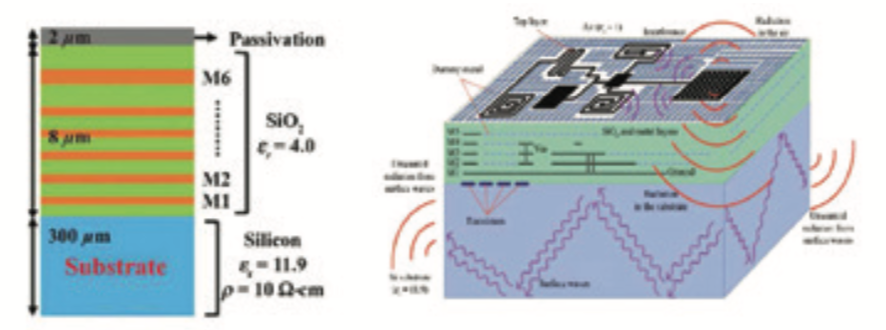

Một ngăn xếp CMOS điển hình được mô tả trong Hình 3. Một đế silicon dày 300÷500 μmm nằm ở phía dưới. Trên bề mặt của đế silicon, các lớp chất điện môi mỏng (dày khoảng 7÷15 μmm) được nhúng với 6÷9 lớp kim loại, mỗi lớp có độ dày khoảng 500 nm, ngoại trừ lớp kim loại trên cùng, có độ dày bằng 1÷2 mm. Các lớp kim loại thường được sử dụng để thực hiện các thành phần thụ động, chẳng hạn như tụ điện, cuộn cảm và đường truyền. Các liên kết cũng được thực hiện trong các lớp kim loại này và sử dụng lỗ via giữa các lớp. Trong số tất cả các lớp kim loại, lớp trên cùng là sự lựa chọn tốt nhất cho thiết bị triển khai OCA vì độ dày kim loại tương đối cao hơn của nó có thể giảm thiểu hiệu ứng bề mặt, đặc biệt là đối với anten ở dải tần sóng mm và sub-terahertz.

Hình 3. Ngăn xếp CMOS dựa trên silicon, Hình 4. Tổng quan về các thách thức hệ thống trên chip và OCA

1.1 Hiệu suất bức xạ thấp

Hiệu suất bức xạ thấp là vấn đề lớn nhất khi thiết kế OCA. Lý do chính cho hiệu suất bức xạ thấp là việc sử dụng chất nền silicon có điện trở thấp trong các quy trình CMOS thương mại. Là một chất bán dẫn, đế silicon có điện trở suất thấp khoảng 10÷15 Ωcm, đây là một lợi thế cho thiết kế vi mạch, vì điện trở suất thấp rất hữu ích để tránh các vấn đề về ngắn mạch (latch-up). Tuy nhiên, việc sử dụng chất nền có điện trở suất thấp là một thảm họa đối với thiết kế OCA. Khi anten được đặt gần trên đế silicon có điện trở suất thấp này, sóng điện từ EM (electromagnetic) sẽ tìm thấy một đường đi có điện trở suất thấp trong đế silicon. Do đó, đế silicon hấp thụ hầu hết công suất RF, được tiêu tán trong đế silicon dưới dạng nhiệt mà không được bức xạ ra không khí[3], như được hiển thị trong Hình 4. Do đó, OCA có hiệu suất bức xạ rất thấp.

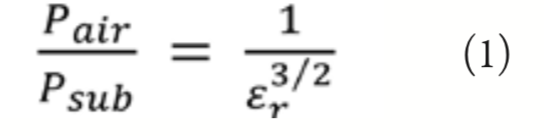

Ngoài đặc tính suy hao cao, đế silicon còn có hằng số điện môi cao là 11,9. Điều này dẫn đến nhiều trường EM hơn trong chất nền so với bức xạ vào không gian tự do. Trên thực tế, tỷ số giữa công suất bị giữ lại trong chất nền so với công suất bức xạ ra không khí có thể được tính gần đúng bằng công thức sau [4]:

trong đó Psub là công suất hấp thụ trong chất nền, và Pair là công suất bức xạ vào không khí. Theo công thức (1), 97% tổng công suất bị hấp thụ bởi chất nền silicon, trong khi chỉ 3% công suất RF được bức xạ trong không khí. Công suất hấp thụ bởi chất nền chủ yếu bị tiêu tán dưới dạng nhiệt và một số được bức xạ từ chất nền theo những hướng không xác định.

1.2 Sóng bề mặt

Ngoài hiệu suất bức xạ thấp, OCA cũng gặp vấn đề tạo ra sóng bề mặt do hằng số điện môi cao và độ dày lớn của chất nền. Các sóng bề mặt bậc cao này làm sai lệch mô hình bức xạ mong muốn của anten. Độ dày điển hình của đế silicon được sử dụng trong chế tạo CMOS nằm trong khoảng 300÷700 μmm, được coi là bề dày điện đối với các ứng dụng tần số sóng mm. Ngoài ra, hằng số điện môi cao của chất nền silicon làm giảm bước sóng truyền trong chất nền. Kết quả là, các sóng bề mặt bậc cao có thể được tạo ra trong chất nền silicon này. Chất nền anten luôn hỗ trợ ít nhất một chế độ (mode) sóng bề mặt. Mode sóng bề mặt này được gọi là mode TM0, không có tần số cắt, vì vậy chúng luôn được kích thích.

Phương trình sau cho thấy tần số cắt sóng bề mặt cho các mode bậc cao hơn:

trong đó n là mode sóng bề mặt (n=0,2,4...đối với modeTMn; n=1,3,5...đốivới chế độ TEn),c là tốc độ ánh sáng trong không gian tự do, h là độ dày của chất nền, và ε là hằng số điện môi của chất nền. Theo công thức (2), độ dày chất nền càng lớn và hằng số điện môi càng cao dẫn đến tần số cắt thấp hơn; do đó, nhiều sóng bề mặt với các mode sóng cao hơn có thể được kích thích. Ví dụ, một OCA ở 77 GHz có thể kích thích sóng

Hình 7. (a) Đồng mô phỏng trong Cadence và (b) đồng mô phỏng trong HFSS; Hình 8. RFIC với các tấm kim loại lấp đầy giả

2.2 Đồng mô phỏng OCA và mạch

Thông thường, thiết kế anten được thực hiện trong trình mô phỏng EM, chẳng hạn như ANSYS HFSS[9] hoặc CST STUDIO SUITE[10], dựa vào việc giải các phương trình Maxwell với các điều kiện biên thích hợp. Mặt khác, các nhà thiết kế mạch không yêu cầu mô phỏng EM và do đó sử dụng các trình mô phỏng như Cadence[11] hoặc Keysight ADS[12] để mô phỏng mạch, thường thực hiện phân tích nút dựa trên điện áp hoặc dựa trên dòng điện.

Có một số công cụ mô phỏng chính thống có thể chạy đồng thời cả EM và mô phỏng mạch, nhưng ngay cả trong các trình mô phỏng này, việc đánh giá ảnh hưởng giữa OCA và các mạch là không hoàn toàn khả thi. Vì lý do này, thiết kế OCA thường được tối ưu hóa lần đầu tiên trong trình mô phỏng EM; sau đó, bố cục của nó được xuất sang một công cụ thiết kế vi mạch, chẳng hạn như Cadence. Tuy nhiên, cấu trúc anten không thể được mô phỏng trong công cụ thiết kế vi mạch, do đó không thể mô phỏng toàn bộ hệ thống (mạch và anten) cùng nhau. Điều này là do trình mô phỏng EM dựa trên việc giải các phương trình Maxwell trong các trường được chia lưới để có được hiệu suất EM chính xác của các cấu trúc 3D. Tuy nhiên, các ảnh hưởng ghép nối và các đặc tính của anten, chẳng hạn như hiệu suất bức xạ, không thể được mô hình hóa và mô phỏng trong trình mô phỏng mạch. Tương tự, không thể mô phỏng biểu diễn mạch trong bộ trình phỏng EM.

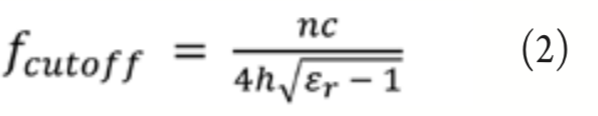

Anten phải được mô phỏng theo cách chính xác như khi nó được kết nối với mạch và ngược lại. Mặc dù rất khó để mô phỏng anten và mạch đồng thời, nhưng vẫn tồn tại một số phương pháp. Phương pháp phổ biến nhất để đánh giá các tác động của OCA đến hiệu suất mạch là trích xuất tham số tán xạ S (S-parameters) của OCA từ trình mô phỏng EM sau khi tối ưu hóa và nhập chúng vào công cụ thiết kế vi mạch. Sau đó, mạch có thể được đồng mô phỏng với các đặc tính trở kháng đầu vào của OCA. Như được trình bày trong Hình 7 (a), các tham số S của OCA được nhập vào Cadence để chạy đồng mô phỏng với bộ dao động điều khiển điện áp trên chip (VCO). Thông thường, nó yêu cầu một số lần lặp lại giữa công cụ thiết kế IC và trình mô phỏng EM để đạt được thiết kế tối ưu hóa với sự phối hợp trở kháng tốt giữa mạch và OCA.

Tuy nhiên, điều này làm tăng đáng kể độ phức tạp và thời gian mô phỏng. Ngoài ra, các tham số S được trích xuất của OCA nằm trong miền tần số và không thể được sử dụng trực tiếp trong phân tích miền thời gian[13]. Thêm vào đó, các tham số S của OCA bị ảnh hưởng bởi trở kháng cổng trong trình mô phỏng EM, vì vậy điều quan trọng là phải đảm bảo rằng trở kháng giao diện phù hợp với trở kháng cổng trong trình mô phỏng EM. Để bao gồm ảnh hưởng của mạch và các cấu trúc kim loại trên chip khác đối với hiệu suất của OCA, phương pháp thông thường là tạo mô hình các cấu trúc kim loại gần nhau, chẳng hạn như các thành phần mạch thụ động, tấm liên kết và tấm lấp đầy kim loại giả trong trình mô phỏng EM để đảm bảo rằng hiệu suất của OCA mô phỏng là đáng tin cậy và chính xác, như được trình bày trong Hình 7 (b).

Tuy nhiên, cách tiếp cận này cũng gặp phải một số thách thức. Đầu tiên, bố trí là giai đoạn cuối cùng của thiết kế vi mạch, và vì thiết kế anten và mạch được thực hiện song song, người thiết kế anten phải tối ưu lại anten sau khi bố trí vi mạch hoàn tất. Thứ hai, mặc dù cách bố trí của phần mạch, bao gồm các thành phần thụ động, tấm liên kết và tấm lấp đầy kim loại giả có thể được nhập trong trình mô phỏng EM từ công cụ thiết kế vi mạch, nhưng các mô hình mạch vẫn không đại diện cho trường hợp thực, vì mạch không hoạt động trong bộ mô phỏng EM. Ví dụ, hiệu ứng ghép nối giữa OCA và cuộn cảm không có dòng điện khác với trường hợp OCA gần cuộn cảm có dòng điện. Ngoài ra, việc bố trí chính xác các cấu trúc kim loại trong mô phỏng EM có thể làm tăng đáng kể thời gian mô phỏng. Hơn nữa, các trình mô phỏng EM không thể tính đến tất cả các thuộc tính trong các quá trình bán dẫn, điều này chỉ có thể được nghiên cứu kỹ trong công cụ thiết kế vi mạch.

Vấn đề này chỉ có thể được giải quyết khi mô phỏng EM toàn sóng và mô phỏng mạch có thể chạy cùng nhau, trong một trình mô phỏng đơn lẻ hoặc hai mô phỏng chạy cùng nhau.

3. Vấn đề bố trí anten trên chip

Trong chu trình thiết kế vi mạch, có một bước quan trọng khác có thể ảnh hưởng đáng kể đến hiệu năng của OCA đó là quá trình bố trí chip, bị hạn chế bởi kiểm tra quy tắc thiết kế DRC (Design Rule Check). Trong giai đoạn này, DRC là một quá trình quan trọng để đảm bảo rằng bố trí chip đáp ứng các quy tắc được xác định bởi các xưởng đúc bán dẫn [14]. Mỗi xưởng đúc bán dẫn có bộ quy tắc riêng để đảm bảo sai số chế tạo.

Trong số hàng trăm quy tắc trong DRC, ba loại quy tắc thiết kế rất quan trọng đối với thiết kế OCA. Đầu tiên là yêu cầu về mật độ kim loại nhất định trong mỗi lớp kim loại vì mật độ kim loại ảnh hưởng đến tốc độ ăn mòn trong giai đoạn chế tạo. Quy tắc mật độ kim loại toàn cục cho biết mật độ kim loại cần thiết cho toàn bộ chip, trong khi quy tắc mật độ cục bộ xác định các yêu cầu mật độ kim loại cho một khu vực nhất định, thường là khu vực 100μm×100μm. Phạm vi mật độ kim loại điển hình là 30%÷70%. Để đáp ứng yêu cầu về mật độ kim loại, một số lượng lớn các “tấm kim loại giả” nên được đặt trong khu vực trống, trong khi nhiều khe (slots) nên được khắc trên bề mặt tấm kim loại lớn. Hình 8 cho thấy các tấm kim loại giả màu xanh lam được đặt trong một khu vực trống ở tất cả các lớp, trong khi một số khe được khắc trên mặt bức xạ lớn màu đen của anten. Khi các khe và tấm kim loại giả được đưa vào vùng OCA, hiệu suất của anten có thể kém đi. Đặc biệt, các tấm kim loại giả gần có thể gây nhiễu không mong muốn với OCA.

Loại quy tắc thiết kế quan trọng thứ hai là quy tắc thiết kế lớp kim loại, cho biết chiều rộng dây kim loại tối đa/tối thiểu, khoảng cách tối thiểu và kích thước tối thiểu của vỏ bọc. Thông thường, các giới hạn dưới của chiều rộng dây, khoảng cách và kích thước vỏ bọc không ảnh hưởng đến hiệu suất OCA, vì chúng ở quy mô nanomet, trong khi anten mmwave và sub-terahertz chỉ yêu cầu độ phân giải chế tạo ở quy mô micromet. Tuy nhiên, giới hạn trên của chiều rộng dây kim loại là khoảng 20÷30 μm, điều này có thể hạn chế tính linh hoạt trong thiết kế anten. Loại thứ ba là quy tắc thiết kế lỗ via, bao gồm các yêu cầu về kích thước của một via và kích thước của mảng via. Trong trường hợp thiết kế OCA gồm nhiều lớp, một kết nối RF chắc chắn giữa các lớp là rất cần thiết, vì vậy kích thước kích thước lỗ via đơn và kích thước mảng via đóng vai trò quan trọng. Một số quy tắc thiết kế khác có thể ảnh hưởng đến OCA. Vì vậy, khi thiết kế OCA, tất cả các quy tắc thiết kế này cần được xem xét và đưa vào mô phỏng một cách thích hợp để tránh sự khác biệt giữa mô phỏng và các phép đo cuối cùng.

4. Đo kiểm OCA

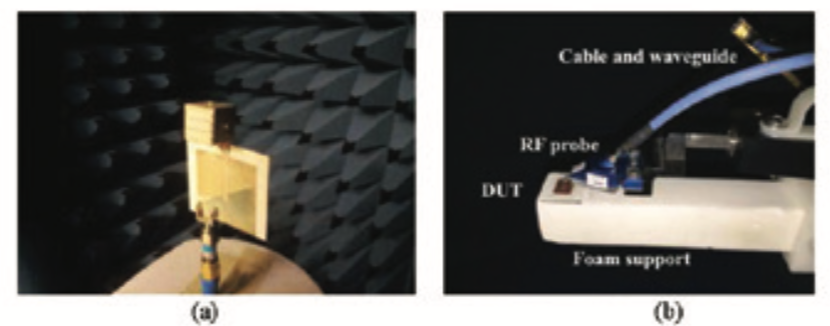

Thông thường, việc chế tạo vi mạch được gia công cho các xưởng đúc CMOS thương mại. Sau khi chip đã sẵn sàng, một bước quan trọng khác là đo kiểm các đặc tính của OCA. Đặc tính của anten thông thường được đo đạc trong một buồng chống dội âm (anechoic chamber) bằng cách kết nối anten với máy phân tích mạng thông qua connector SMA, như được trình bày trong Hình 9 (a). Phương pháp đo sử dụng connector SMA thuận tiện và chính xác để đo các anten tương đối lớn; tuy nhiên, điều này không khả thi đối với việc xác định đặc tính của OCA. Kích thước của connector và chân tín hiệu của nó tương ứng trên quy mô vài cm và mm, trong khi kích thước của OCA thường vài trăm micromet, tùy thuộc vào tần số hoạt động của chúng. Hơn nữa, các tấm đệm RF để đo OCA thậm chí còn nhỏ hơn, thường trong phạm vi từ 50×50 μm2 đến 100×100 μm2. Trong trường hợp này, OCA quá nhỏ để kết nối qua connector SMA.

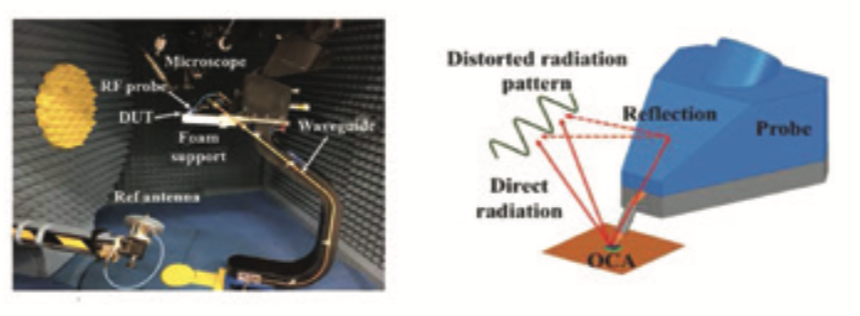

Do đó, thay vì sử dụng connector SMA, một đầu dò RF thường được sử dụng để tiếp xúc vào OCA, như được hiển thị trong Hình 9 (b). Đầu dò RF được chế tạo đặc biệt để đặt trên các tấm đệm RF của RFIC và OCA. Các đầu cực nhỏ của đầu dò RF có thể được đặt chính xác trên các tấm đệm RF với sự trợ giúp của kính hiển vi. Các OCA không thể được kiểm tra trong các buồng chống dội tiêu chuẩn; do đó, cần phải có các buồng chuyên dụng, chi phí rất cao, như được minh họa trong Hình 10. Được bao phủ bởi một bộ hấp thụ EM, buồng chứa một đĩa xoay hướng theta/phi được gắn với anten tham chiếu, một cánh tay cố định để đặt đầu dò và đặt OCA ở trung tâm buồng và kính hiển vi là một phần của hệ thống thị giác để đảm bảo độ chính xác khi đặt đầu dò trên miếng đệm chip. Mặc dù một buồng không dội âm như vậy có thể xác định đặc tính của hệ số phản xạ và mô hình bức xạ của OCA nhưng vẫn còn một số thách thức liên quan đến độ chính xác của phép đo dựa trên đầu dò này.

Hình 9. Phương pháp đo anten: (a) dựa vào connector và (b) dựa trên đầu dò

Trong tất cả các thách thức liên quan đến việc xác định đặc tính OCA dựa trên đầu dò, sự can nhiễu giữa đầu dò RF và OCA được coi là quan trọng nhất. Như được mô tả trong Hình 9 (b), đầu dò RF bao gồm một thân dây dẫn lớn và các đầu của đầu dò được gắn vào một cánh tay kim loại, được bao phủ một phần bởi bộ hấp thụ EM. Với sự hiện diện của thân dây dẫn lớn gần đầu dò RF, sóng EM sẽ bị phản xạ từ thân đầu dò. Sóng EM bức xạ từ anten và sóng phản xạ từ thân dây dẫn đầu dò can nhiễu với nhau. Mô hình bức xạ cuối cùng là sự chồng chất của sóng bức xạ và sóng phản xạ. Các bức xạ cực đại và cực tiểu có thể thu được ở các góc nhất định, tùy thuộc vào độ lệch pha giữa sóng bức xạ và sóng phản xạ [15], như được trình bày trong Hình 11.

Kết quả là, mô hình bức xạ của OCA bị bóp méo do sự hiện diện của thân dây dẫn của đầu dò. Ngoài ảnh hưởng đến mô hình bức xạ của anten, nhiễu không mong muốn giữa OCA và thân dây dẫn của đầu dò và các đầu dò không được che đậy có thể gây ra những thay đổi không mong muốn trong hệ số phản xạ, mặc dù trở kháng bên trong của đầu dò đã được khử qua hiệu chuẩn trở kháng [16]. Một thách thức khác liên quan đến việc xác định đặc tính anten dựa trên đầu dò là khả năng tự bức xạ của chính đầu dò. Như trước đây đã đề cập, các đầu của đầu dò không được bao phủ bởi bộ hấp thụ EM. Vì bản thân đầu dò RF cũng bức xạ, nên mô hình bức xạ cuối cùng là sự chồng chất của mô hình bức xạ OCA và mô hình bức xạ của đầu dò [17]. Để khảo sát sự tự bức xạ của đầu dò, mô hình bức xạ của đầu dò được đo khi đầu dò được kết nối với tải 50 Ω hiệu chuẩn, đại diện cho một anten phù hợp. Trong trường hợp này, chỉ có bức xạ không đáng kể xuất hiện từ tải 50 Ω, do đó, mẫu bức xạ đo được có thể được coi là sự tự bức xạ của đầu dò. Mô hình bức xạ đo được của một đầu dò 60 GHz được trình bày trong [17], cho thấy mức tăng tối đa của tự bức xạ của đầu dò là gần -21 dBi.

Mức tối đa này xác định độ nhạy đo độ lợi của hệ thống đo dựa trên đầu dò. Sự tự bức xạ của đầu dò này là không đáng kể đối với phép đo anten có độ lợi cao; tuy nhiên, nó là đáng kể đối với phép đo các anten có độ lợi thấp, chẳng hạn như OCA. Do độ khuếch đại của OCA thấp, sự tự bức xạ của đầu dò có thể so sánh với độ lợi của anten, do đó gây ra sự không chính xác trong đặc tính mô hình bức xạ của OCA. Một nhược điểm khác của việc xác định đặc tính OCA dựa trên đầu dò là bức xạ của OCA bị chặn bởi thân đầu dò và cánh tay đỡ của nó. Do đó, không thể thu được mô hình bức xạ hoàn chỉnh bằng phương pháp đo dựa trên đầu dò.

Hình 10. Thiết lập đặc trưng OCA dựa trên đầu dò trong phòng chống dội μ-lab; Hình 11. Can nhiễu giữa bức xạ của OCA và phản xạ từ đầu dò

Kết luận

OCA mang lại nhiều lợi ích cho hệ thống RF như chi phí thấp, kích thước vật lý nhỏ, trọng lượng nhẹ và tiêu thụ điện năng thấp, tạo điều kiện thuận lợi cho việc hiện thực hóa các thiết bị di động nhỏ gọn. Tuy nhiên, các thách thức trong quá trình chế tạo OCA vẫn tồn tại. Thách thức đầu tiên là hiệu suất bức xạ anten thấp và sóng bề mặt xảy ra do chất nền silicon có điện trở suất thấp và hằng số điện môi cao, dẫn tới năng lượng điền từ bức xạ từ anten bị hấp thụ bởi chất nền. Tiếp đến là ảnh hưởng ghép nối giữa anten và mạch làm hiệu suất làm việc của chúng bị giảm.

Việc bố trí anten trên chip kích thước nhỏ cũng là một thách thức khác trong khi vẫn phải đảm bảo các nguyên tắc thiết kế DRC. Cuối cùng, việc đo kiểm OCA không thể thực hiện thông qua connector SMA thông thường mà cần sử dụng đầu dò, điều này làm giảm độ chính xác trong việc đo các tham số của anten do ảnh hưởng của đầu dò. Trong tương lai, các giải pháp khắc phục các thách thức này sẽ được nghiên cứu.

Tài liệu tham khảo:

1. R. T. Rao, System on Package: Miniaturization of the Entire System. New York: McGraw-Hill Education (in Eng), 2008.

2. Y. P. Zhang and D. Liu, "Antenna-on-Chip and Antenna-in-Package Solutions to Highly Integrated Millimeter-Wave Devices for Wireless Communications," IEEE Transactions on Antennas and Propagation, vol. 57, no. 10, pp. 2830–2841, 2009, doi: 10.1109/ TAP.2009.2029295.

3. H. M. Cheema and A. Shamim, "The Last Barrier: On-Chip Antennas," IEEE Microwave Magazine, vol. 14, no. 1, pp. 79–91, 2013, doi: 10.1109/MMM.2012.2226542.

4. A. Babakhani, X. Guan, A. Komijani, A. Natarajan, and A. Hajimiri, "A 77-GHz Phased-Array Transceiver With On-Chip Antennas in Silicon: Receiver and Antennas," IEEE Journal of Solid-State Circuits, vol. 41, no. 12, pp. 2795–2806, 2006, doi: 10.1109/JSSC.2006.884811.

5. L. Marnat, A. A. A. Carreno, D. Conchouso, M. G. Martı ́nez, I. G. Foulds, and A. Shamim, "New Movable Plate for Efficient Millimeter Wave Vertical on-Chip Antenna," IEEE Transactions on Antennas and Propagation, vol. 61, no. 4, pp. 1608–1615, 2013, doi: 10.1109/TAP.2013.2241720.

6. J. Briaire and S. Krisch, "Principles of Substrate Crosstalk Generation in CMOS Circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 19, no. 6, pp. 645–653, 2000, doi:10.1109/43.848086.

7. T. Deng and Y. P. Zhang, "On-Chip Antennas," in Handbook of Antenna Technologies, Z. N. Chen, D. Liu, H. Nakano, X. Qing, and T. Zwick Eds. Singapore: Springer, 2016, pp. 1565–1584.

8. S. Uemura, Y. Hiraoka, T. Kai, and S. Dosho, "Isolation Techniques Against Substrate Noise Coupling Utilizing Through Silicon Via (TSV) Process for RF/Mixed-Signal SoCs," IEEE Journal of Solid-State Circuits, vol. 47, no. 4, pp. 810–816, 2012, doi: 10.1109/ JSSC.2012.2185169.

9. Ansys.com. (n.d.). ANSYS HFSS: High Frequency Electromagnetic Field Simulation Software. [Online] Available at: https://www.ansys.com/products/electronics/ansys-hfss.

10.CST Studio Suite 3D EM Simulation and Analysis Software. [Online] Available at: http:// www.cst.com.

11. Cadence: EDA Tools and IP for Intelligent System Design. [Online] Available at: https:// www.cadence.com.

12. Keysight: PathWave Advanced Design System (ADS). [Online] Available at: https://www. keysight.com/zz/en/products/software/pathwave-design-software/pathwave-advanced- design-system.html.

13. Y. Zhang, N. H. W. Fong, D. C. W. Ng, and N. Wong, "Co-simulation of RFIC with bondwire antenna via retarded PEEC method," in 2012 IEEE International Symposium on Circuits and Systems (ISCAS), 20–23 May 2012, pp. 229–232, doi: 10.1109/ISCAS.2012.6271751.

14. Qammer H. Abbasi, Syeda F. Jilani, Akram Alomainy and Muhammad a. Immran, "Antennas and Propagation for 5G and beyond," the institution of engineering and technology, Chapter 6, 2020.

15. L. Boehm, M. Hitzler, F. Roos, and C. Waldschmidt, "Probe influence on integrated antenna measurements at frequencies above 100 GHz," in 2016 46th European Microwave Conference (EuMC), 4–6 Oct. 2016 2016, pp. 552–555, doi: 10.1109/EuMC.2016.7824402.

16. H. Zhang and A. Shamim, "Tackling the issues of millimeter-wave on-chip antenna measurements," in 2019 13th European Conference on Antennas and Propagation (EuCAP), 31 Mar.–5 Apr. 2019 2019, pp. 1–5.

17. S. Ranvier, M. Kyro ̈, C. Icheln, C. Luxey, R. Staraj, and P. Vainikainen, "Compact 3-D On-Wafer Radiation Pattern Measurement System for 60 GHz Antennas," COST 2100, Pervasive Mobile & Ambient Wireless Communications, vol. 51, no. 2, pp. 319–324, 2009, doi: 10.1002/mop.24034.

(Bài đăng ấn phẩm in Tạp chí TT&TT số 5 tháng 5/2021)