"Scaling" và cơ hội cho Việt Nam trong công nghệ vi mạch

ChatGPT ra mắt cuối năm ngoái báo hiệu giai đoạn phát triển bùng nổ của thị trường khai thác ứng dụng các mô hình trí tuệ nhân tạo (AI) với quy mô được dự báo nhiều nghìn tỷ USD trong 10 năm tới. Chính những thị trường mới đó đang là những động cơ thúc đẩy sự phát triển của ngành công nghiệp vi mạch.

Vi mạch đã, đang và sẽ thay đổi cách chúng ta làm việc, tương tác

Trong khoảng 20 năm nữa, có lẽ vi mạch sẽ vượt xa mọi con số hay dự báo có thể có của chúng ta tại thời điểm hiện tại. Vi mạch đã, đang và sẽ thay đổi cách chúng ta làm việc, cách chúng ta tương tác và có thể thay đổi cả sức khỏe và hạnh phúc của chúng ta trong tương lai. Mặt khác, công nghệ sản xuất chip hiện tại cũng đang đi tới điểm tới hạn của công nghệ, đòi hỏi sự thay đổi phương thức thiết kế, chế tạo sản phẩm vi mạch, đặc biệt vấn đề “scaling” đang đứng trước những thách thức vô cùng lớn.

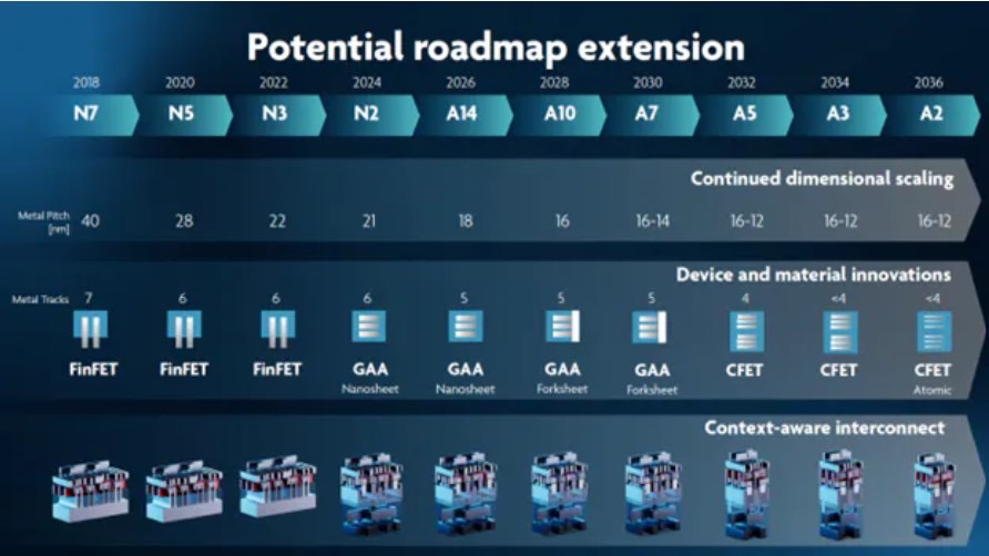

Trong ngành bán dẫn, phát biểu nổi tiếng của Gordon Moore vào năm 1965 mà cốt lõi của nó có thể tóm gọn trong từ “scaling”, đã dẫn dắt sự phát triển của lĩnh vực chip trong suốt thời gian qua. Các hãng như TSMC, Samsung, Intel cùng với IBM, IMEC đã nỗ lực rất nhiều để hiện thực hóa phát biểu của Moore. Nhưng hiện nay các hãng như TSMC, Intel, Samsung cần nhiều thới gian hơn 18 tháng để có thể đưa ra một tiến trình công nghệ mới. Trong khi đó, AI, ô tô tự lái, kết nối thông minh,… tạo ra nhu cầu tăng gấp đôi sức mạnh tính toán sau mỗi 3,5 tháng, nhanh hơn nhiều so với phát biểu của định luật Moore.

Tương lai của “scaling” trong công nghệ vi mạch

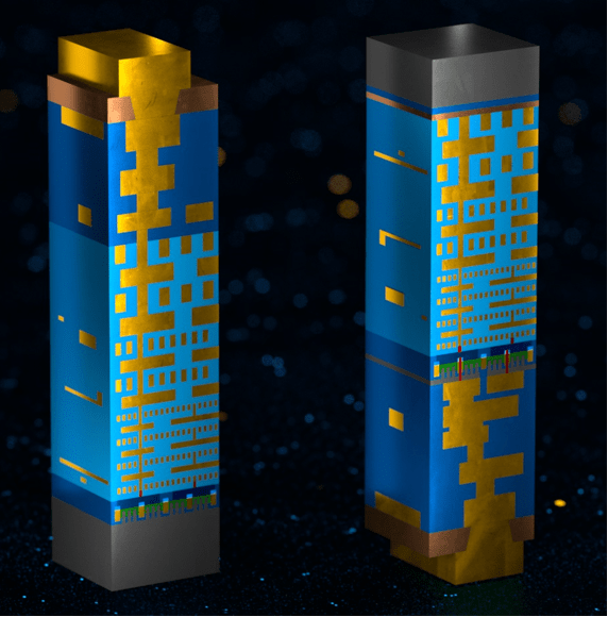

Lời giải cho bài toán này có thể là chúng ta sẽ không thúc đẩy “scaling” trong không gian tính theo đơn vị diện tích (2D) nữa mà chuyển sang thúc đẩy “scaling” theo không gian tính theo đơn vị thể tích (3D). Xu thế tích hợp không đồng nhất (heterogeneous integration) đang dần trở thành công nghệ chủ đạo và nó cũng đặt ra các bài toán về hiệu quả kiểm soát chất lượng của các vi mạch sản xuất ở các tiến trình công nghệ khác nhau, cũng như độ tin cậy trong quá trình tích hợp.

Các hệ thống ở “không gian 3 chiều” chắc chắn sẽ dẫn tới sự thay đổi trong cách thức hoạt động của ngành, khác với mô hình chuyên môn hóa từng khâu chuyên biệt rồi ghép chúng lại theo các tiêu chuẩn định sẵn một cách độc lập khép kín, giờ đây toàn bộ hệ sinh thái điện tử cần làm việc cùng nhau để tạo ra chúng hay ít nhất là cùng nhau làm việc để thống nhất ra các tiêu chuẩn chung mới.

Quang khắc là khâu quan trọng có tính quyết định trong suốt quá trình “in” hàng loạt chip lên tấm wafer nền. Với mỗi lớp vật liệu, quang khắc được sử dụng để tạo khuôn mẫu trên bề mặt wafer sau đó sẽ là các bước lắng đọng, ăn mòn, cấy ion, …; và lại lặp lại sử dụng quang khắc cho việc in các lớp vật liệu tiếp theo; có khoảng vài chục lần lặp lại như vậy cho mỗi mẻ sản xuất. Kiểm soát được tỷ lệ xuất hiện lỗi trong quá trình sản xuất là tâm điểm vấn đề kỹ thuật trong các nhà máy sản xuất các tiến trình công nghệ tiên tiến.

Cách thông thường nhất là tiến hành đo đạc mức độ chính xác trong quá trình tạo khuôn mẫu để điểu chỉnh. Và khi yêu cầu chính xác tới kích thước nano mét thì điều này là thách thức kỹ thuật vô cùng khó, nó đòi hỏi độ chính xác tuyệt đối ở quá trình tạo mẫu mỗi lớp. Điều này dẫn tới hệ quả là giá thành một bộ khuôn để đúc chip ở tiến trình công nghệ tiên tiến và các máy móc sử dụng trong đó đã trở nên vô cùng đắt đỏ, đi ngược lại giá trị cốt lõi của “scaling” truyền thống là ngày càng làm giảm giá thành chế tạo của một transistor.

Thêm nữa, các ứng dụng trong tương lai cần sức mạnh tính toán vô cùng lớn, điều này tất yếu sẽ dẫn tới sự tiêu tốn năng lượng. Để đáp ứng yêu cầu về sức mạnh tính toán, tốc độ truyền dẫn, tuổi thọ bộ nhớ trong khi vẫn đảm bảo các yêu cầu về vấn đề tản nhiệt, hay điện áp cung cấp không vượt quá tính chất lý hóa vốn có của vật liệu bán dẫn dựa trên silicon hiện tại, đội ngũ kỹ thuật đang đứng trước một khối lượng công việc mới khổng lồ đối với quá trình chuyển đổi quy trình công nghệ, dây chuyền sản xuất, lắp ráp và đóng gói.

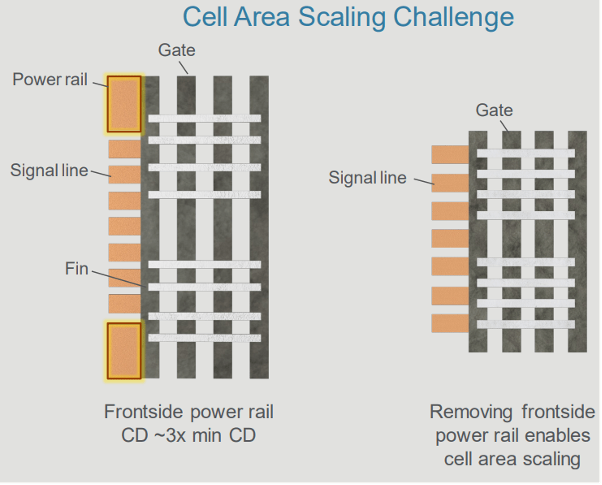

Khi tích hợp nhiều hơn số lượng linh kiện trong một đơn vị diện tích đồng nghĩa với việc số lượng các lớp dây dẫn kim loại để kết nối các tín hiệu tăng lên, khi tổng chiều dài dây dẫn tăng và số lớp vật liệu dây dẫn kim loại tăng lên thì vấn đề tín hiệu truyền dẫn bị trễ gây nên bởi mạng lưới kết nối đường dẫn tín hiệu sẽ ngày càng trở nên nghiêm trọng. Ngoài ra để đảm bảo nguồn điện cung cấp từ bên ngoài tới được các linh kiện không bị suy giảm, thì mạng lưới dây dẫn kim loại dẫn điện từ chân cấp nguồn tới các cực của linh kiện sẽ là tác nhân chiếm nhiều không gian làm cho việc scaling ngày càng khó khăn hơn.

Với đặc tính điện trở suất thấp và độ tin cậy cao của vật liệu kim loại đã giúp đồng trở nên phổ biến trong ngành công nghiệp bán dẫn nhưng các chip hiện nay cần tới hơn 14 lớp kết nối kim loại trong khi kích thước mỗi chiều của chip vượt quá 10mm thì độ trễ gây ra bởi các dây liên kết vật liệu đồng (RC) thậm chí còn lớn hơn độ trễ của nội tại gây ra bởi các phần tử logic, tức là thời gian tín hiệu chạy trên dây dẫn còn lớn hơn thời gian để phần tử logic tính toán, điều này nhiều khi làm cho việc scaling (giảm nhỏ kích thước phần tử logic) mất đi ý nghĩa. Để có thể giảm được đỗ trễ này hoặc chúng ta phải tìm kiếm kim loại có tính chất dẫn điện tốt hơn để thay thế kim loại đồng (ví dụ Rutheni) hoặc làm ngắn chiều dài các đường kết nối lại.

Một ý tưởng đột phá để giảm độ trễ RC và giúp vấn đề tản nhiệt tốt hơn là chế tạo mạng lưới cung cấp nguồn điện ở mặt sau của wafer và dành toàn bộ không gian mặt trước cho các lớp kết nối tín hiệu. Điều này sẽ tạo thêm nhiều không gian dùng cho các đường kết nối tín hiệu đồng thời cải thiện điện trở của mạng lưới cung cấp nguồn điện bằng việc sử dụng các đường dẫn kim loại có chiều rộng lớn hơn ở mặt sau của các phần tử logic. Lý do dẫn tới ý tưởng này là do các đường dẫn tín hiệu và dây dẫn nguồn có những yêu cầu kỹ thuật khác nhau: cung cấp nguồn điện cần mạng lưới đường dây to có điện trở thấp nhưng với dây tín hiệu, chúng ta cần dây dẫn có tiết diện nhỏ điện dung thấp và ngắn. Mâu thuẫn này được giải quyết triệt để với ý tưởng đột phá nói trên.

Việc loại bỏ các đường kết nối nguồn điện ở mặt trước tạo ra nhiều không gian cho các kết nối tín hiệu, nghĩa là cùng một đơn vị diện tích có thể đặt thêm nghiều phần tử logic hơn, hoặc cùng một số lượng phần tử logic, chúng ta cần ít hơn không gian cho việc kết nối giữa các cổng tín hiệu của các phần tử logic. Kết quả là việc này có thể giúp “scaling” các phần tử logic thêm 20% - 30% như mô tả ở hình 3 dưới đây.

Tuy nhiên, cách tiếp cận kết nối mạng lưới phân phối nguồn điện ở mặt sau của các phần tử logic đặt ra yêu cầu cần mài mỏng phiến bán dẫn dẫn tới độ dày ~10um (so với độ dày bình thường ~300um), điều này làm giảm sức chịu đựng va đập của phiến bán dẫn, dẫn đến các thách thức mới trong quy trình đóng gói. Nhưng những thách thức này không làm thay đổi sự hấp dẫn của việc có thể tiếp tục tăng mật độ các đường liên kết giúp duy trì tốc độ “scaling” trong ngành vi mạch bán dẫn.

“Scaling” theo không gian tính theo đơn vị thể tích (3D); kỹ thuật quang khắc; hay kết nối mạng lưới cung cấp nguồn điện ở mặt sau wafer là ba trong số vô cùng nhiều các ví dụ cho các thay đổi trong kỹ thuật thiết kế, chế tạo vi mạch đang diễn ra rất sôi động hiện nay. Sự đổi mới tiếp cận mọi khía cạnh trong toàn ngành, chưa bao giờ các nhà thiết kế chip phải nói chuyện với nhà sản xuất và đóng gói nhiều như vậy.

Chip đang ngày càng trở nên cần thiết hơn, đa dạng hơn và đáng tin cậy hơn, định luật Moore tiếp tục là động lực thúc đẩy chi phối sự phát triển của cả lĩnh vực. Công nghệ chip chuyển sang thế hệ mới có thể coi là cơ hội để Việt Nam rút ngắn và bắt kịp về trình độ của nguồn nhân lực nếu chúng ta có thể tranh thủ tích lũy và hấp thụ càng nhiều càng tốt về con người, kỹ thuật, mô hình kinh doanh, … để ngày càng bồi đắp xây dựng được thương hiệu cạnh tranh cốt lõi về chất lượng nguồn nhân lực như ý kiến chỉ đạo của Thủ tướng Chính phủ Phạm Minh Chính trong buổi làm việc mới đây với Đại học Quốc gia Hà Nội về việc tập trung phát triển nguồn nhân lực chất lượng cao, khi đó lĩnh vực vi mạch sẽ có đóng góp lớn cho sự phát triển chung của Việt Nam trong tương lai ./.

.jpg)

.jpg)